俹俬俠亅倀俽俛俬俷丂倳倱倝値倗丂俛俙俽俬俠

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

倀俽俛僀儞僞乕僼僃乕僗傪撪憼偟偨俹俬俠傪巊偭偰倂倝値倓倧倵倱僷僜僐儞偱奜晹夞楬傪惂屼偡傞偨傔偺奺庬俬乛俷婎斅偺惢嶌婰帠偱偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞侾俆俉夞乶

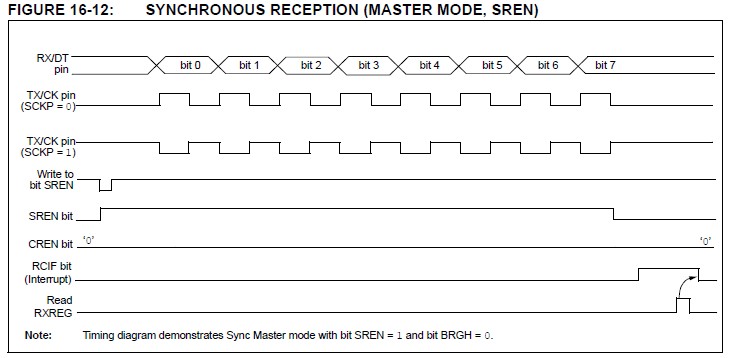

仠俹俬俠倀俽俛俬俷亅侽俁乮侾侽俈乯俤倀俽俙俼俿乮俋乯摨婜儌乕僪乮俀乯儅僗僞乕庴怣儌乕僪

慜夞偼摨婜儅僗僞乕憲怣儌乕僪偵偮偄偰愢柧偟傑偟偨丅

崱夞偼摨婜儅僗僞乕庴怣儌乕僪偱偡丅

乵弌揟乶俵倝們倰倧們倛倝倫丂俿倕們倛値倧倢倧倗倷丂俬値們丏丂俹俬俠侾俉俥侾俁俲俆侽乛侾係俲俆侽丂俢倎倲倎丂俽倛倕倕倲

仠摨婜儅僗僞乕庴怣儌乕僪

僨乕僞偼俼倃乛俢俿抂巕偱庴怣偟傑偡丅

俼倃乛俢俿抂巕偺弌椡僪儔僀僶偼俤倀俽俙俼俿傪摨婜儅僗僞乕庴怣儌乕僪偵愝掕偟偨偲偒偼懳墳偡傞俿俼俬俽價僢僩傪僙僢僩偟偰乮乫侾乫偵偟偰乯柍岠偵偟側偗傟偽側傝傑偣傫丅

摨婜儌乕僪偱偼庴怣偼僔儞僌儖庴怣僀僱乕僽儖價僢僩乮俼俠俽俿俙儗僕僗僞偺俽俼俤俶乯偐宲懕庴怣僀僱乕僽儖價僢僩乮俼俠俽俿俙儗僕僗僞偺俠俼俤俶乯傪僙僢僩偡傞偙偲偱僀僱乕僽儖乮桳岠乯偵側傝傑偡丅

俽俼俤俶傪僙僢僩偟偰俠俼俤俶傪僋儕傾偡傞偲侾暥帤價僢僩暘偺悢偺僋儘僢僋偩偗偑惗惉偝傟傑偡丅

俽俼俤俶價僢僩偼侾暥帤偺庴怣偑姰椆偡傞偲帺摦揑偵僋儕傾偝傟傑偡丅

俠俼俤俶傪僙僢僩偡傞偲僋儘僢僋偼俠俼俤俶傪僋儕傾偡傞傑偱宲懕偟偰惗惉偝傟傑偡丅

暥帤僨乕僞傪庴怣偟偰偄傞搑拞偱俠俼俤俶傪僋儕傾偡傞偲俠俲抂巕偺僋儘僢僋偼捈偪偵掆巭偝傟庴怣搑拞偺暥帤僨乕僞偼攋婞偝傟傑偡丅

俽俼俤俶偲俠俼俤俶傪嫟偵僙僢僩偡傞偲嵟弶偺暥帤僨乕僞偺庴怣傪姰椆偟偨偲偒偵俽俼俤俶偑僋儕傾偝傟偰偦傟埲屻偼俠俼俤俶偩偗偑桪愭揑偵宲懕偝傟傑偡丅

庴怣傪奐巒偡傞偵偼俽俼俤俶偐俠俼俤俶傪僙僢僩偟傑偡丅

俼倃乛俢俿抂巕偐傜擖椡偝傟傞僨乕僞偼俿倃乛俠俲僋儘僢僋偺壓偑傝僄僢僕偱僒儞僾儕儞僌偝傟偰庴怣僔僼僩儗僕僗僞乮俼俽俼乯偵僔僼僩擖椡偝傟傑偡丅

庴怣暥帤僨乕僞偑俼俽俼偵姰慡偵僔僼僩擖椡偝傟傞偲俼俠俬俥價僢僩偑僙僢僩偝傟偦偺僨乕僞偼俀暥帤暘偺庴怣俥俬俥俷偵憲傜傟傑偡丅

俼俠俼俤俧傪撉傓偲庴怣俥俬俥俷偺僩僢僾偺僨乕僞偑撉傒弌偝傟傑偡丅

俼俠俬俥偼庴怣俥俬俥俷偵枹撉僨乕僞偑巆偭偰偄傞娫偼僙僢僩偝傟偨傑傑偵側傝傑偡丅

乵弌揟乶俵倝們倰倧們倛倝倫丂俿倕們倛値倧倢倧倗倷丂俬値們丏丂俹俬俠侾俉俥侾俁俲俆侽乛侾係俲俆侽丂俢倎倲倎丂俽倛倕倕倲

仠僗儗乕僽僋儘僢僋

摨婜僨乕僞捠怣偱偼僨乕僞儔僀儞偺傎偐偵僨乕僞偵摨婜偡傞僋儘僢僋儔僀儞傪巊偄傑偡丅

僗儗乕僽僨僶僀僗偼俿倃乛俠俲儔僀儞偺僋儘僢僋傪庴怣偟傑偡丅

俿倃乛俠俲抂巕偺弌椡僪儔僀僶偼俤倀俽俙俼俿偑摨婜僗儗乕僽憲怣傑偨偼僗儗乕僽庴怣儌乕僪偵愝掕偝傟偰偄傞偲偒偼懳墳偡傞俿俼俬俽價僢僩傪僙僢僩偟偰乮乫侾乫偵偟偰乯柍岠偵偟側偗傟偽側傝傑偣傫丅

僔儕傾儖僨乕僞價僢僩偼僋儘僢僋偺棫偪忋偑傝僄僢僕偛偲偵曄壔偟傑偡丅

僨乕僞價僢僩偼僋儘僢僋僒僀僋儖偛偲偵憲弌偝傟傑偡丅

僨乕僞價僢僩偺悢偩偗偺僋儘僢僋偑庴怣偝傟傑偡丅

乵弌揟乶俵倝們倰倧們倛倝倫丂俿倕們倛値倧倢倧倗倷丂俬値們丏丂俹俬俠侾俉俥侾俁俲俆侽乛侾係俲俆侽丂俢倎倲倎丂俽倛倕倕倲

仠庴怣僆乕僶乕儔儞僄儔乕

庴怣俥俬俥俷僶僢僼傽偼俀暥帤暘偺僨乕僞傪曐帩偱偒傑偡丅

俥俬俥俷偵俀暥帤暘偺僨乕僞偑偁偭偰枮攖偺忬懺偺偲偒偵俼俠俼俤俧偑傾僋僙僗偝傟傞慜偵偦偙偵俁斣栚偺僨乕僞偑棃傞偲僆乕僶乕儔儞僄儔乕偑敪惗偟丄俼俠俽俿俙儗僕僗僞偺俷俤俼俼價僢僩偑僙僢僩偝傟傑偡丅

俥俬俥俷偵偁傞僨乕僞偼忋彂偒偝傟傑偣傫丅

偡偱偵俥俬俥俷僶僢僼傽偵偁傞俀暥帤暘偺僨乕僞偼撉傒弌偣傑偡偑僄儔乕偑夝徚偝傟傞傑偱偼怴偟偄暥帤僨乕僞偼庴怣偱偒傑偣傫丅

俷俤俼俼價僢僩偼僆乕僶儔儞忬懺偑夝徚偝傟傞傑偱偼僋儕傾偱偒傑偣傫丅

俽俼俤俶價僢僩偑僙僢僩偝傟偰偄偰俠俼俤俶偑僋儕傾偝傟偰偄傞偲偒偵僆乕僶乕儔儞僄儔乕偑敪惗偟偨偲偒偼丄偦偺僄儔乕偼俼俠俼俤俧傪撉傓偙偲偱僋儕傾偝傟傑偡丅

俠俼俤俶價僢僩偑僙僢僩偝傟偰偄傞偲偒偵僆乕僶乕儔儞僄儔乕偑敪惗偟偨偲偒偼丄偦偺僄儔乕忬懺偼俼俠俽俿俙儗僕僗僞偺俠俼俤俶價僢僩傪僋儕傾偡傞偐丄俽俹俤俶價僢僩傪僋儕傾偟偰俤倀俽俙俼俿傪儕僙僢僩偡傞偙偲偱夝徚偝傟傑偡丅

乵弌揟乶俵倝們倰倧們倛倝倫丂俿倕們倛値倧倢倧倗倷丂俬値們丏丂俹俬俠侾俉俥侾俁俲俆侽乛侾係俲俆侽丂俢倎倲倎丂俽倛倕倕倲

仠摨婜儅僗僞乕庴怣偺僙僢僩傾僢僾

侾丏俽俹俛俼俧俫偍傛傃俽俹俛俼俧儗僕僗僞偵抣傪愝掕偟傑偡丅

丂丂揔愗側僨僶僀僗儃乕儗乕僩傪愝掕偡傞偨傔偵俛俼俧俫偍傛傃俛俼俧侾俇價僢僩傪僙僢僩丄僋儕傾偟傑偡丅

俀丏俽倄俶俠丄俽俹俤俶偍傛傃俠俽俼俠偺奺價僢僩傪僙僢僩偟偰摨婜儅僗僞乕僔儕傾儖億乕僩傪僀僱乕僽儖乮桳岠乯偵偟傑偡丅

丂俼倃乛俢俿偍傛傃俿倃乛俠俲偺弌椡僪儔僀僶偼懳墳偡傞俿俼俬俽價僢僩傪僙僢僩偡傞乮乫侾乫偵偡傞乯偙偲偱柍岠偵偟傑偡丅

俁丏俠俼俤俶偍傛傃俽俼俤俶價僢僩偑僋儕傾偝傟偰偄傞偙偲傪妋擣偟傑偡丅

係丏杮峞偱偼妱崬傒偼埖偄傑偣傫偺偱偙偺崁偼徣棯偟傑偡丅

俆丏杮峞偱偼俋價僢僩儌乕僪偼埖偄傑偣傫偺偱偙偺崁偼徣棯偟傑偡丅

俇丏俽俼俤俶價僢僩傪僙僢僩偡傞偐丄宲懕庴怣傪偡傞偨傔偵俠俼俤俶價僢僩傪僙僢僩偡傞偙偲偵傛偭偰庴怣傪奐巒偟傑偡丅

俈丏杮峞偱偼妱崬傒偼埖偄傑偣傫偺偱偙偺崁偼徣棯偟傑偡丅

俉丏俼俠俽俿俙儗僕僗僞傪撉傓偙偲偱僄儔乕偑敪惗偟偰偄傞偐偳偆偐傪妋擣偟傑偡丅

俋丏俼俠俼俤俧儗僕僗僞傪撉傫偱俉價僢僩偺庴怣僨乕僞傪庢摼偟傑偡丅

侾侽丏傕偟傕僆乕僶乕儔儞僄儔乕偑敪惗偟偨傜丄俼俠俽俿俙儗僕僗僞偺俠俼俤俶價僢僩傪僋儕傾偡傞偐丄俽俹俤俶價僢僩傪僋儕傾偟偰俤倀俽俙俼俿傪儕僙僢僩偡傞偙偲偱僄儔乕傪僋儕傾偟傑偡丅

摨婜儅僗僞乕庴怣儌乕僪攇宍恾

乵弌揟乶俵倝們倰倧們倛倝倫丂俿倕們倛値倧倢倧倗倷丂俬値們丏丂俹俬俠侾俉俥侾俁俲俆侽乛侾係俲俆侽丂俢倎倲倎丂俽倛倕倕倲

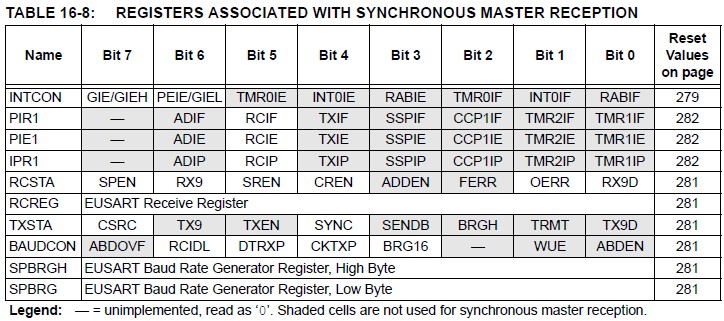

摨婜儅僗僞乕庴怣偵娭學偡傞儗僕僗僞偺堦棗昞

乵弌揟乶俵倝們倰倧們倛倝倫丂俿倕們倛値倧倢倧倗倷丂俬値們丏丂俹俬俠侾俉俥侾俁俲俆侽乛侾係俲俆侽丂俢倎倲倎丂俽倛倕倕倲

亅亖枹幚憰丅乫侽乫偑撉傒弌偝傟傞丅傾儈偺偐偐偭偨價僢僩偼摨婜儅僗僞乕庴怣偱偼巊梡偝傟側偄丅

俹俬俠亅倀俽俛俬俷丂倳倱倝値倗丂俛俙俽俬俠乵戞侾俆俉夞乶

俀侽俀俁丏侾丏侾俈倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞