トランジスタで8080をつくってしまおうというまさにびっくり仰天、狂気のプロジェクトです!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

見事にできましたら、もちろんTK-80モニタを乗せて、それからBASIC、CP/Mを走らせましょう!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

[第437回]

●バイナリカウンタ回路の改良(14)

[第426回]以降でトランジスタロジック回路のオープンコレクタについて考えました。

その結果として[第430回]で「TR05」回路基板を製作し[第431回]では「TR03」回路基板を製作しました。

当連載記事としてはその後はまた「バイナリカウンタ回路」の再検討について書いてきたのですが、試作基板としては「TR05」、「TR03」以外にも製作したものが何点かあります。

その多くはオープンコレクタがらみの回路です。

試作基板は先日出来上がって手元にあるのですがまだほとんど手がついていません。

これから検証していくことになります。

「バイナリカウンタ回路」についてもオープンコレクタ化した試作基板を製作したのですがその時点では「エッジパルス」方式にこだわっていたため今となってはその方式で製作した試作基板は無用のものになってしまいました。

そんなわけで「バイナリカウンタ」のオープンコレクタ試作基板としては使える基板は手元にないのですが、ちょうど前回、前々回でずっと以前に作ったバイナリカウンタ基板を利用して試作を行なった基板が手元に使える状態であります。

そこで前回テストで利用した基板にさらに手を加えてオープンコレクタの動作テストを行いました。

すでに何回か書いていますようにトランジスタロジック回路をオープンコレクタ化すると出力に大きな遅れが出ます。

遅れを小さくするにはプルアップ抵抗の値を小さくするなどの対策が必要です。

プルアップ抵抗を小さくするとトランジスタがONしているときの消費電流が増加します。

[第426回]ではCPU回路では同時にアクティブになるラインは限られているのでそれほど心配することはないと書きましたがいささか浅慮でした。

たとえばRSフリップフロップの場合片方がOFFのときにもう片方はONになります。

ということはオープンコレクタで構成したRSフリップフロップではその回路個数分の電流が常時流れることになります。

それはトランジスタ数の削減とはまた別の問題になってきます。

トランジスタのオープンコレクタについては回路全体の消費電流についてもあわせて検討する必要があります。

しかし。

回路を考える前から消費電流のために及び腰になってしまっては先に進むことができません。

ここは消費電流について忘れないでおくこととしたうえでロジック回路としての適否について考えていくことにします。

それで。

今回は前回の回路をもとにしてその一部をオープンコレクタに置き換えて動作するかどうかを確認してみました。

最初に検討したのは下の回路です。

①の回路をオープンコレクタにして試してみたのですがこれは駄目でした。

オープンコレクタにすることでV側とG側の時間差が大きくなってしまうことが原因ではないかと思いますがよくわかりません。

とにかくここは前回と同じ回路のままにします。

②をオープンコレクタにすることには無理があります。

ここも前回と同じ回路にします。

オープンコレクタにするとすれば③の回路ということになります。

RSフリップフロップ2段の回路です。

前回の回路では2個のRSフリップフロップのそれぞれを2SA1015と2SC1815各1個で構成したインバータ(74LS04相当)を2回路組み合わせることでフリップフロップ回路にしていました。

今回はそこを2SC1815だけのオープンコレクタで構成しました。

全部で4個使っていた2SA1015のうちの2個を抵抗で置き換えましたが残り2個は抵抗での置き換えもせず完全に外しました。

それでも動作することは実験で確かめました。

R14はプルアップ抵抗ではないのですがそこ(T4とT10)にはプルアップ抵抗はなくてもよいという結果になりました。

T2とT8についてはCKINの周波数をうんと落とせばよいのですがある程度以上の周波数ではプルアップ抵抗が必要です。

RSフリップフロップの前段と後段でプルアップ抵抗の値にも差があって前段(T2)のほうがより小さな値の抵抗値が必要です。

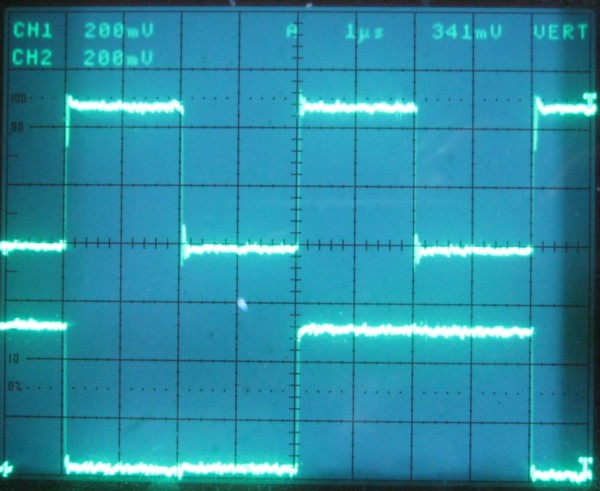

下は上の回路のQ_の出力波形です。

上側(CH1)は入力クロック(CKIN)です。

下側(CH2)はQ_出力です。

今までのテストに比べるとかなり低い入力周波数(31.25KHz)です。

これより高い入力周波数ではフリップフロップとして働きません。

下は上の回路のQ出力波形です。

下側(CH2)がQ出力です。

次に試した下の回路は上の回路とほとんど同じです。

R7(T8のプルアップ抵抗)も1KΩにしたところだけが異なっています。

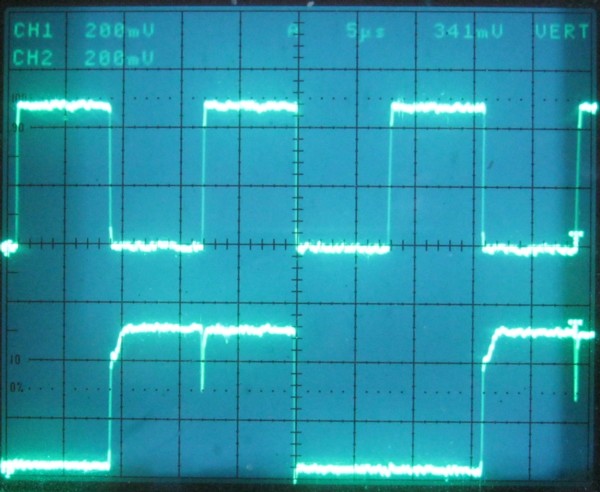

下は上の回路のQ_の出力波形です。

上側(CH1)は入力クロック(CKIN)です。

下側(CH2)はQ_出力です。

上のテストより少し高い入力周波数(62.5KHz)です。

これより高い入力周波数ではフリップフロップとして働きません。

下は上の回路のQ出力波形です。

下側(CH2)がQ出力です。

バイナリカウンタ回路は多ビットの構成になります。

上位ビットになるにつれて入力クロックの周波数が低くなりますからそのあたりをふまえて柔軟な回路構成にするときに上のテスト結果を参考にすることができると思います。

今回のテストをしていく過程で③の前段のフリップフロップの上側のトランジスタが入力周波数を上げるために大きなウェイトを占めていることがわかってきました。

そこで入力クロックの周波数が高いところではそこはオープンコレクタにしないで前回と同じ回路とすることを考えました。

③のT1(2SA1015)のみを前回と同じように実装しました。

T8のプルアップ抵抗R7は4.7KΩ、T4とT10はプルアップ抵抗はありません。

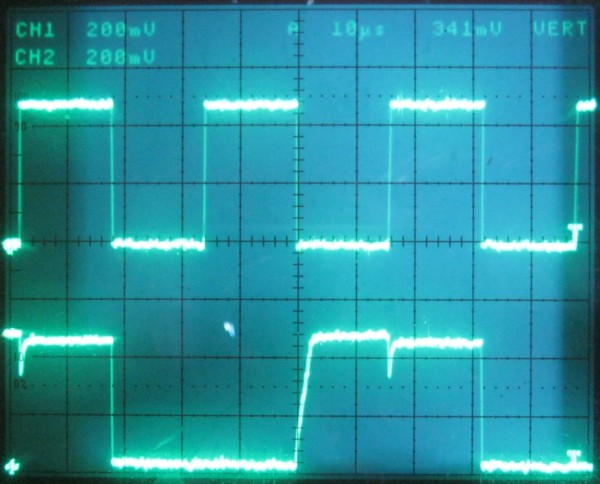

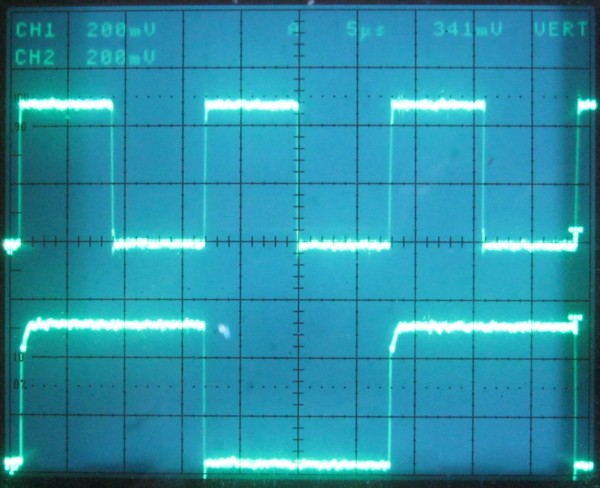

下は上の回路のQ_の出力波形です。

上側(CH1)は入力クロック(CKIN)です。

下側(CH2)はQ_出力です。

上のテストよりも高い周波数(250KHz)です。

これより高い周波数ではフリップフロップとして働きません。

波形がゆがんでいるのは入力周波数がこの回路としては限界に近いからです。

もう少し低い周波数では波形は改善します。

下は上の回路のQ出力波形です。

下側(CH2)がQ出力です。

Q出力はきれいな波形になります。

R7を1KΩにしました。

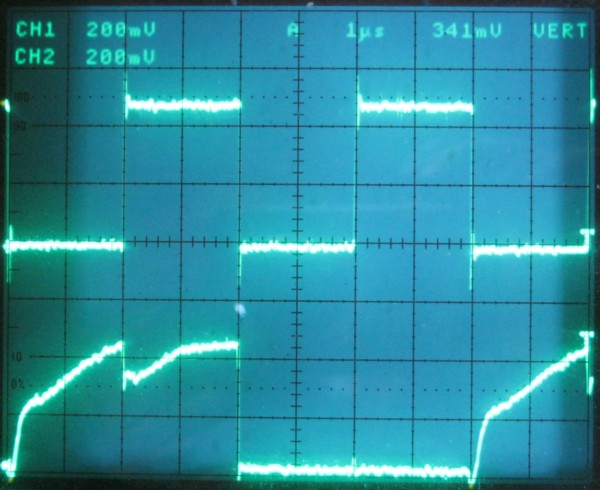

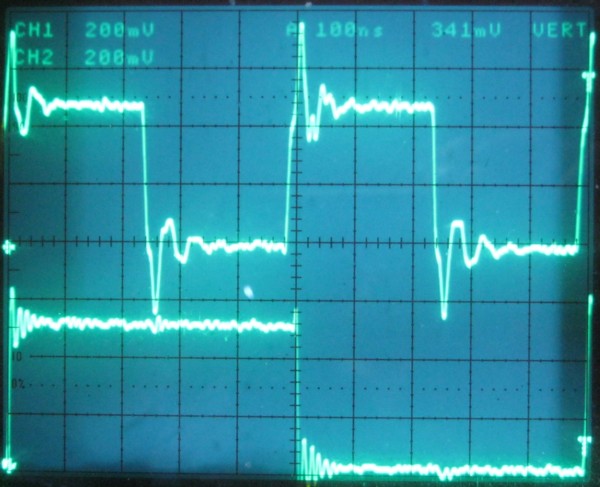

下は上の回路のQ_の出力波形です。

上側(CH1)は入力クロック(CKIN)です。

下側(CH2)はQ_出力です。

前回までの回路での最高の入力周波数(2MHz)です。

この回路としては入力周波数が上限に近いため波形がかなりなまっています。

もう少し低い周波数では波形は改善します。

下は上の回路のQ出力波形です。

下側(CH2)がQ出力です。

今までと同様Q出力はきれいな波形になります。

T1だけではなくT7も2SA1015を実装しました。

前段のRSフリップフロップも後段のRSフリップフロップも上(前)のフリップフロップは前回までと同じ2SA1015と2SC1815で構成し下(後)のフリップフロップは2SC1815だけでプルアップ抵抗なしのオープンコレクタです。

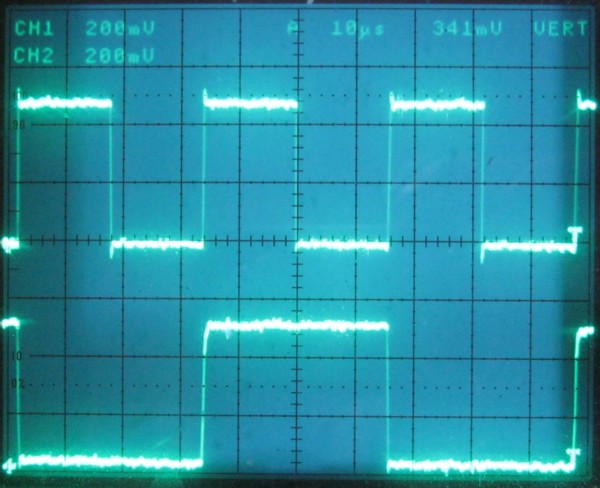

下は上の回路のQ_の出力波形です。

上側(CH1)は入力クロック(CKIN)です。

下側(CH2)はQ_出力です。

前回までの回路での最高の入力周波数は2MHzです。

それと同じ入力周波数2MHzでもきれいな波形です。

下は上の回路のQ出力波形です。

下側(CH2)がQ出力です。

こちらもきれいな波形です。

トランジスタでCPUをつくろう![第437回]

2024.3.27upload

前へ

次へ

ホームページトップへ戻る