トランジスタで8080をつくってしまおうというまさにびっくり仰天、狂気のプロジェクトです!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

見事にできましたら、もちろんTK-80モニタを乗せて、それからBASIC、CP/Mを走らせましょう!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

[第436回]

●バイナリカウンタ回路の改良(13)

前回説明しましたトランジスタの逆接続対策のためのダイオード追加回路についてさらに考えてみました。

前回書きましたようにトランジスタのエミッタにダイオードを追加するという案は[第201回]で考えたものでした。

ところで[第201回]を再読してみますとダイオードを追加したのはトランジスタが逆接続(2SC1815の場合エミッタに+5Vがかかる状態でベースがH、コレクタがLになる状態)になるのを防ぐというよりもエミッタに別のビットのラインからの電圧がかかることで逆電流が流れてしまうのを防ぐことが目的だと書いています。

結果的に逆接続対策になっているのでそれはそれでよいのですけれど。

ずっと論じていますバイナリカウンタ回路は[第201回]で問題としている回路とは異なり他のビットからの電圧がかかるということはありません。

前回エミッタにダイオードを追加したのは純粋にエミッタに+5V(2SC1815の場合です。2SA1015の場合はGND電位)が直接かかることを防止するためです。

しからば。

逆接続になっては本当にいかんのか?

本来ならば避けるべきであることはわかっています。

そこを敢えて無視したら本当にいけないのか。

その疑問です。

そこを敢えて無視してしまうとこういう回路になります。

ダイオードを外してしまいました。

すっきりした回路になります。

これはまさに悪魔の誘惑であります。

この回路ではトランジスタ(②のT1、T2、T5、T6)が逆接続になる期間が出てきます。

例として②のT6のエミッタに+5Vがかかっているときを考えてみます。

CKG2=Vccの状態です。

このときに逆接続になるのはベース電位がHでコレクタ((B)点)がLのときです。

このときは③のT9、T10のコレクタもLのときですからT6が逆接続のためエミッタからコレクタに逆電流が流れて(B)点の電位が上がります。

このとき(B)点の電圧はどの位になるのか、それを推測してみることにします。

トランジスタの逆接続については逆電流以前にVEBO耐圧の問題があります。

それについては後で検討することにします。

一般的な2SC1815(2SA1015も同じ)の順方向でのhFE(電流増幅率)は100倍程度です。

逆接続の場合には電流増幅率が1/10以下になるといわれています。

メーカーのデータシートにはその値はありません。

メーカーとしては「危険なのでそれはやるな」というスタンスのようです。

仮にそれが10倍に低下したと考えます。

するとこのときT6のエミッタからコレクタには1mA程度の逆電流が流れることになります。

ということは。

T6の出力インピーダンスは5KΩということです。

R14=4.7KΩですから、すると(B)点は2.5Vほどになってしまいます。

これはアウトです。

だとすれば。

R14を小さくしなければなりません。

たとえばR14=1KΩで考えてみます。

すると(B)点は0.8V程度になりますから、それならセーフです。

しかしここは諸刃の剣です。

通常の順接続の場合の電流増幅率は100倍程度ですからそのときのT6の出力インピーダンスは0.5KΩ程度になります。

するとそのときの(B)点は3.3V程度になります。

1.7V低下することになります。

ぎりぎりセーフかという値です。

もっともその場合にはそれは一瞬で直後に③のT9出力がHになり(B)=5Vになるので不安定な状態ではなくなります。

仮にR=1.5KΩだとすれば逆接続のとき(B)≒1.15V、順接続では(B)≒3.75Vになります。

1.25Vの低下です。

落としどころとしてはそんなところかという感じです。

なんだかちょっと危ない感じになってきました。

カギは逆接続時の電流増幅率ということになります。

そういうことになると。

実験をして試してみるしかありませんでしょう。

実際に上の回路で実験をしてみました。

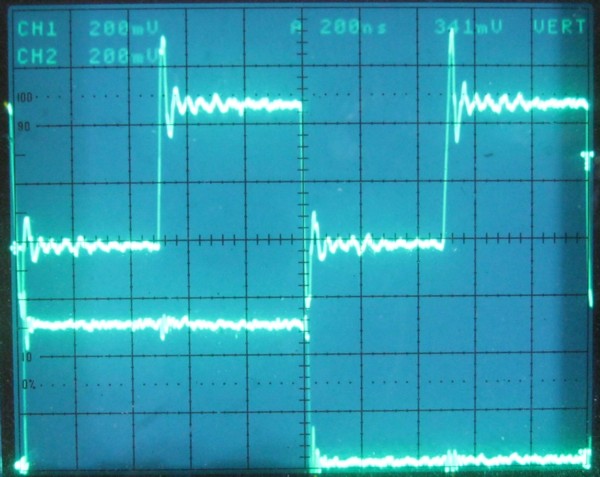

上側(CH1)はCKIN(1MHz)です。

下側(CH2)はQ_出力です。

Q_は入力クロック(CKIN)がLの期間に後段のフリップフロップ(回路図で③の下側のRSFF)に読み込まれるので入力クロックの下がりエッジで変化しています。

安定した出力が得られています。

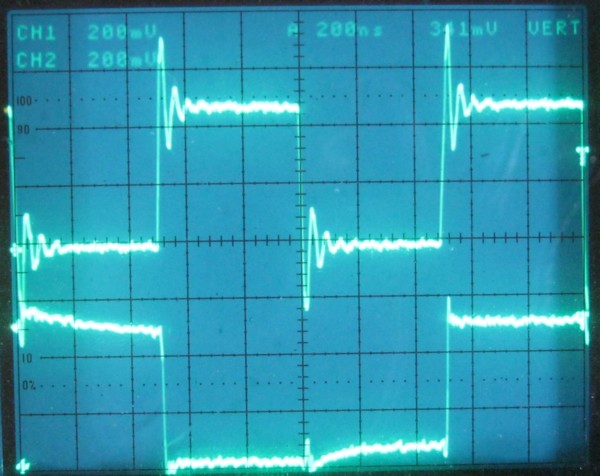

下は回路図の(A)点の波形です。

上側(CH1)はCKIN(1MHz)です。

下側(CH2)は(A)点の波形です。

こちらは入力クロックの立ち上がりで変化しています。

CKIN=Lのときが逆接続になります。

最初のCKIN=LのときのCH2の波形はHなのでちょっとわかりにくいです。

2番目のCKIN=LのときにCH2が少し浮き上がっているようです。

しかしそれはわずかで1V以下のように見えます。

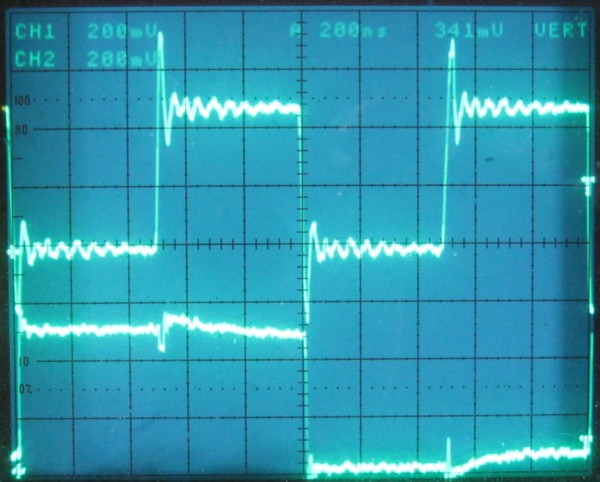

下は回路図の(B)点の波形です。

上側(CH1)はCKIN(1MHz)です。

下側(CH2)は(B)点の波形です。

こちらは入力クロックの立ち下がりで変化しています。

CKIN=Hのときが逆接続になります。

こちらも最初のCKIN=HのときのCH2の波形はHなのでちょっとわかりにくいです。

2番目のCKIN=HのときにはCH2が少し浮き上がっているようです。

こちらもわずかで0.5V程度のように見えます。

案ずるよりも産むが易しです。

試してみた結果では逆接続時の電流増幅率はせいぜい5倍程度のようです。

これなら使えるじゃありませんか。

もう少し安全サイドで考えるならR14=3.3KΩにしてもいいかもしれません。

さて。

問題はVEBOです。

VEBOは逆接続時の耐圧です。

一般にトランジスタのVEBOは小さくて2SA1015、2SC1815では5Vとされています。

Vcc=5Vでは耐圧ぎりぎりです。

絶対最大定格ですから厳密に考えれば一瞬でもサージがあればアウトです。

最悪の場合トランジスタが破損します。

危ないじゃないの。

まあ。

そうなのですけれど。

何十mAも流そうというのではありません。

せいぜい1mA程度です。

絶対最大定格とは言いながら実際のところ工業製品なのですからマージンがゼロということはありませんでしょう。

ここは。

やってみるべきではありませんでしょうか。

おお。

そうでした。

ずっとずっと昔。

初心者だったころ。

先輩が教えてくれた回路を思い出しました。

なんじゃこりゃあ。

露骨に逆接続です。

一瞬にして破損する?

実はこれゼナーダイオードの代用なのです。

まあアマチュア規格です。

ゼナーダイオードの手持ちがないときなどに重宝します。

Voutは大体8Vぐらいで安定したゼナー特性があります。

絶対最大定格を完全に越えてしまっていますから中には壊れてしまうものもあるかもしれませんが。

初心者のころはいろんなトランジスタで結構使ったようでしたが破損したという記憶はありません。

そういうことからすると。

Vcc=5Vなら使えるのではありませんでしょうか。

トランジスタでCPUをつくろう![第436回]

2024.3.26upload

前へ

次へ

ホームページトップへ戻る