トランジスタで8080をつくってしまおうというまさにびっくり仰天、狂気のプロジェクトです!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

見事にできましたら、もちろんTK-80モニタを乗せて、それからBASIC、CP/Mを走らせましょう!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

[第435回]

●バイナリカウンタ回路の改良(12)

1ヶ月以上に亘って検討してきましたエッジパルス方式でのバイナリカウンタ回路は残念ながら断念せざるを得ない結果になってしまいました。

エッジパルス方式にこだわってしまった気持ちの中にはTTLロジックICのフリップフロップとしてはエッジトリガが一般的(だからそうすべき)という思い込みがありました。

この機会にそもそもの当初の回路に戻ってよくよく考えてみました。

よくよく考えてみましたら。

少なくともトランジスタロジック回路に限ってみればそこまでエッジトリガにこだわる必要はなかったのでした。

確かにクロックの立ち上がりの一瞬でフリップフロップの値をラッチするというのは一面では安定した回路であるかのように思えます。

それでは[第411回]の「改良前」の回路はどうかといいますと。

実はこちらの回路でも見方を変えれば半分は「エッジトリガ」だといえます。

この回路の動作については[第166回]で説明をしています。

そこでの説明図で太線の部分が「ラッチデータ」です。

その太線が始まる直前のクロックエッジでデータがラッチされています。

「真性」のエッジトリガと違うところは太線ではない細線の期間はデータが筒抜けになってしまう点です。

この期間にデータにノイズが乗ればそのまま出力に出てしまいます。

ま、しかし。

そんなことがあればそれはCPU回路としては致命的ですから、それはないというのがそもそもの前提になります。

だとすれば「真性」のエッジトリガであろうとなかろうとどちらでもよいことなのでは?

そのように考えて、あらためて「改良前」の回路に戻って考えてみました。

その結果たどりついたのが下の回路です。

回路をわかり易くするため今までと同様CLR回路は外して考えています。

「改良前」の回路ではCLRを別にするとトランジスタを20個使っていました。

今回の回路では一部のトランジスタをダイオードに置き換えましたからトランジスタは16個になりました。

その代わりにダイオードが4個追加になりました。

ダイオードがないとトランジスタのエミッタコレクタ間が逆電位になってしまいます。

するとエミッタからコレクタに通常とは逆向きに電流が流れてしまいます。

ダイオードはそれを防ぐためのものです。

エミッタにダイオードを追加することでコレクタから出力される波形の電圧が+側とGND側のそれぞれで0.7Vほど狭くなります。

この回路に限っていえばそのコレクタからの出力(図中(A)、(B))は「内側」の回路に出力されるもので外部に出力されるものではありませんし、この回路としてはそれは特に問題となるほどのものではありません。

実はこの回路は今回初めて考えたものではありません。

逆接続を回避するための方法としてトランジスタのエミッタ側にダイオードを追加する案について[第201回]で説明をしています。

この方法はエミッタからコレクタへの逆電流は阻止できますがベースからコレクタへの逆電流は阻止できません。

そこで[第411回]の「改良前」の回路では2SA1015と2SC1815の各コレクタのところにクロックによってON/OFFするトランジスタを入れたのでした。

しかしベースとコレクタが逆電位の場合にベースからコレクタに流れる逆電流(2SC1815の場合です。2SA1015の場合にはコレクタからベースに流れる逆電流)は0.1mA程度ですからその程度ならば無視してもよいのではと思います。

今回はそのように判断してあえてトランジスタを置かずに[第201回]の通りエミッタ側にダイオードを置きました。

上でも書きましたように今回の回路は[第411回]の「改良前」の回路に比べてトランジスタが4個減ってダイオードが4個増えました。

わずかな増減のようですが減るのはトランジスタだけではなくて抵抗とコンデンサも各4個減ります。

もともとバイナリカウンタ回路は多段で使用するのが目的ですからたとえば8ビットカウンタで32トランジスタ、16ビットカウンタで64トランジスタの削減(抵抗、コンデンサも同数の削減)ということになればそれなりに有意義な改良ということになると思います。

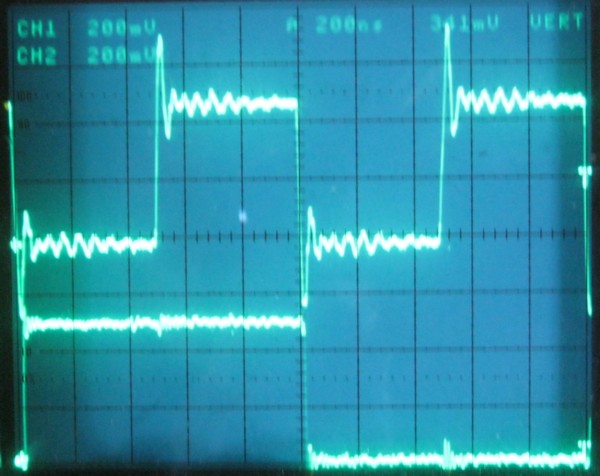

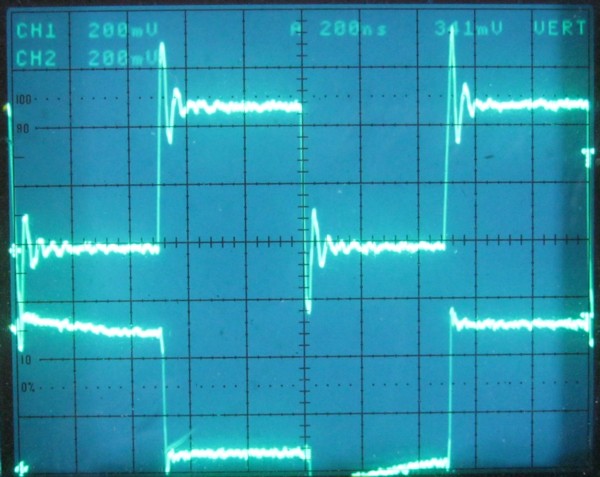

念のために試作を行なって波形をオシロで観測しました。

上側(CH1)はCKIN(1MHz)です。

下側(CH2)はQ_出力です。

Q_は入力クロック(CKIN)がLの期間に後段のフリップフロップ(回路図で③の下側のRSFF)に読み込まれるので入力クロックの下がりエッジで変化しています。

入力クロックのエッジにかなり大きなオーバーシュート、アンダーシュートが見られます。

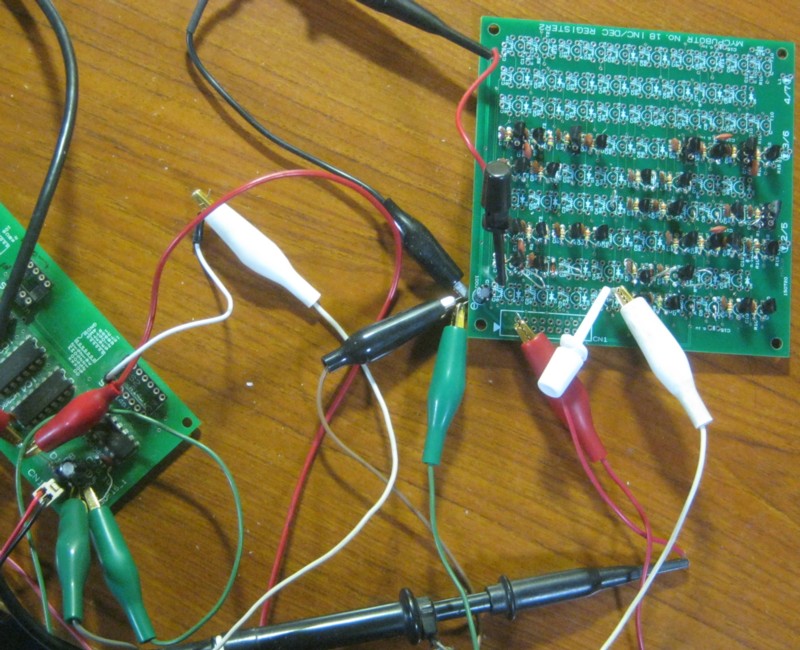

これは下の写真のように電源ラインをケーブルで引き回したりしているからです。

黒と緑のクリップがGND、赤が+5Vです。

右側が今回のテスト回路です。

何年か前に作った試作基板を利用しています。

左側はクロック発生基板です。

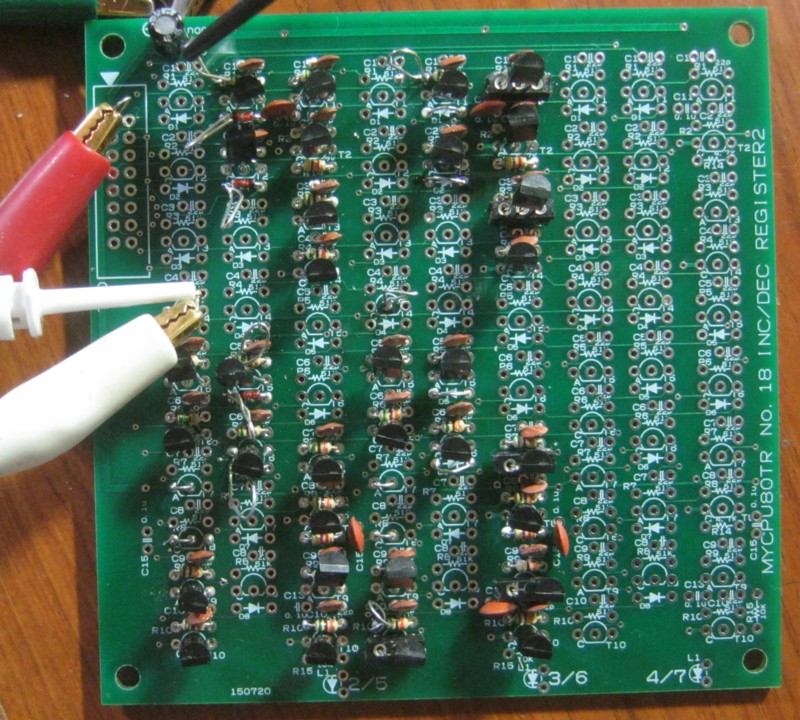

下は試作した回路です。

今回の回路は写真で見て縦3列で1回路です。

回路図の①が第1列、②が第2列、③が第3列です。

今回書いたこと以外にもあれこれテストをするために同じ回路をもう1回路組みました。

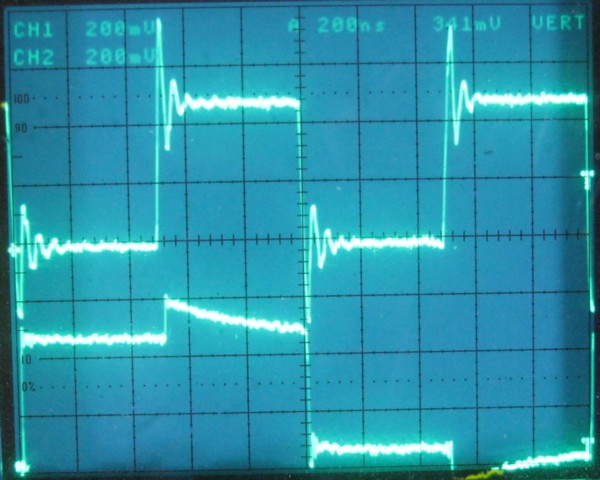

下は回路図の(A)点の波形です。

上側(CH1)はCKIN(1MHz)です。

下側(CH2)は(A)点の波形です。

こちらは入力クロックの立ち上がりで変化しています。

波形にはダイオードの影響とおそらくはエミッタ・ベース間の逆電流の影響が出ているようです。

下は回路図の(B)点の波形です。

上側(CH1)はCKIN(1MHz)です。

下側(CH2)は(B)点の波形です。

こちらは入力クロックの立ち下がりで変化しています。

こちらも波形にはダイオードの影響とおそらくはエミッタ・ベース間の逆電流の影響が出ているようです。

トランジスタでCPUをつくろう![第435回]

2024.3.25upload

前へ

次へ

ホームページトップへ戻る