俹俬俠俛俙俽俬俠僐儞僷僀儔

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

傑傞偱僀儞僞僾儕僞丅偱傕僐儞僷僀儔偱偡丅挻僇儞僞儞挻僔儞僾儖偱偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞侾侽係夞乶

仠俽俢僇乕僪俬俥乮俀係乯俶俢俉侽倅俁丏俆偵愙懕乮侾俈乯夝寛曇乮俀乯

慜夞偐傜偺懕偒偱偡丅

乽榑傛傝徹嫆乿偲偄偆尵梩偑偁傝傑偡丅

慜夞偼偁傟偙傟帋偟偰峫偊偨寢壥傂偲偮偺悇榑偵摓払偟傑偟偨丅

偟偐偟偦傟偩偗偱偼偨偩偺悇應丄棟孅偵夁偓傑偣傫丅

悇應偟偨側傜偽師偵偼偦傟傪幚嵺偵妋偐傔偰傒傞昁梫偑偁傝傑偡丅

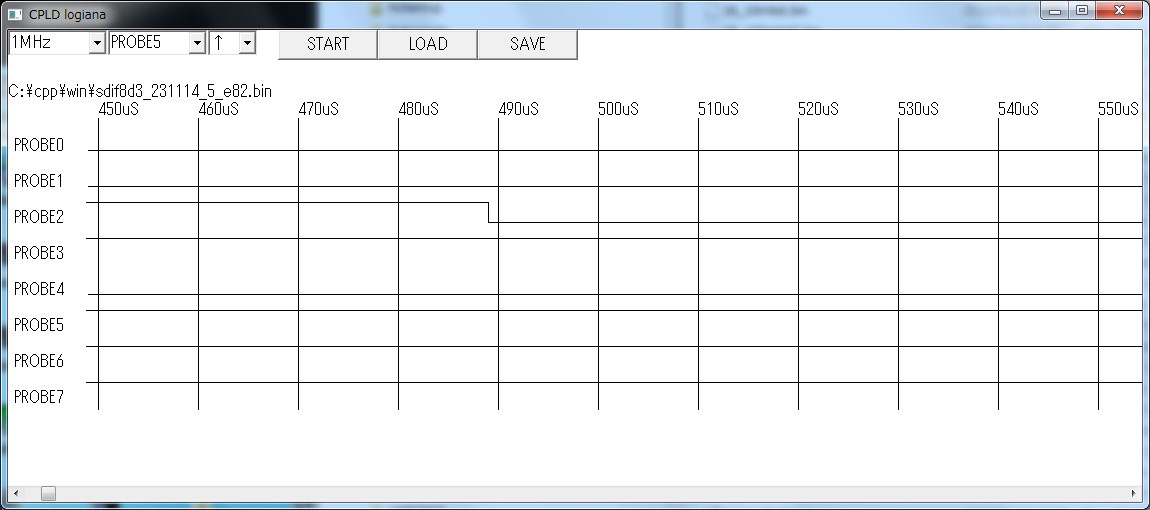

壓偼慜夞悇應偟偨俶俢俉侽倅俁丏俆偲俹俬俠侾俉俥俀俆俆侽偺婲摦帪偺捠怣儔僀儞偺攇宍偱偡丅

俹俬俠侾俉俥俀俆俆侽偑俿俼俬俽俙柦椷偱俹俷俼俿俙傪弌椡偵愝掕偟偨偲偒偺弌椡傪俶俢俉侽倅俁丏俆偑偦傟埲屻偵弌椡偝傟傞偼偢偺攇宍偲岆擣偟偰偟傑偆壜擻惈傪帵嵈偟偨僠儍乕僩偱偡丅

偦傟偵偼忦審偑偁傝傑偡丅

慜夞偼彂偒楻傜偟偰偟傑偄傑偟偨偑忋婰偺栤戣偼偍偦傜偔揹尮搳擖屻偺嵟弶偺僾儘僌儔儉幚峴帪偵偼敪惗偣偢丄揹尮傪擖椡偟偨傑傑侾夞栚偺僾儘僌儔儉傪幚峴帪丄堦扷僾儘僌儔儉偺幚峴傪廔椆偟偨偁偲傆偨偨傃俀夞栚偵僾儘僌儔儉傪幚峴偟偰偦偙偱俹俬俠侾俉俥俀俆俆侽偺儕僙僢僩偑峴側傢傟偨応崌偵尷偭偰敪惗偡傞偲偄偆偙偲偱偡丅

幚嵺偵偦傟偼孞傝曉偟偰僥僗僩傪偡傞偙偲偵傛偭偰妋擣偱偒偰偄傑偡丅

偦偟偰侾夞栚偺僾儘僌儔儉傪幚峴偟偨偲偒偵傕偦偺僾儘僌儔儉傪廔椆偡傞捈慜偵俹俬俠侾俉俥俀俆俆侽偑幚峴偡傞柦椷偵偼偁傞忦審偑偁傝傑偡丅

偦偺偙偲偵偮偄偰偼屻傎偳専徹偟傑偡丅

傑偢偼乽榑傛傝徹嫆乿偱偡丅

偙偙偼傗偭傁傝俠俹俴俢儘僕傾僫偺弌斣偱偁傝傑偟傚偆丅

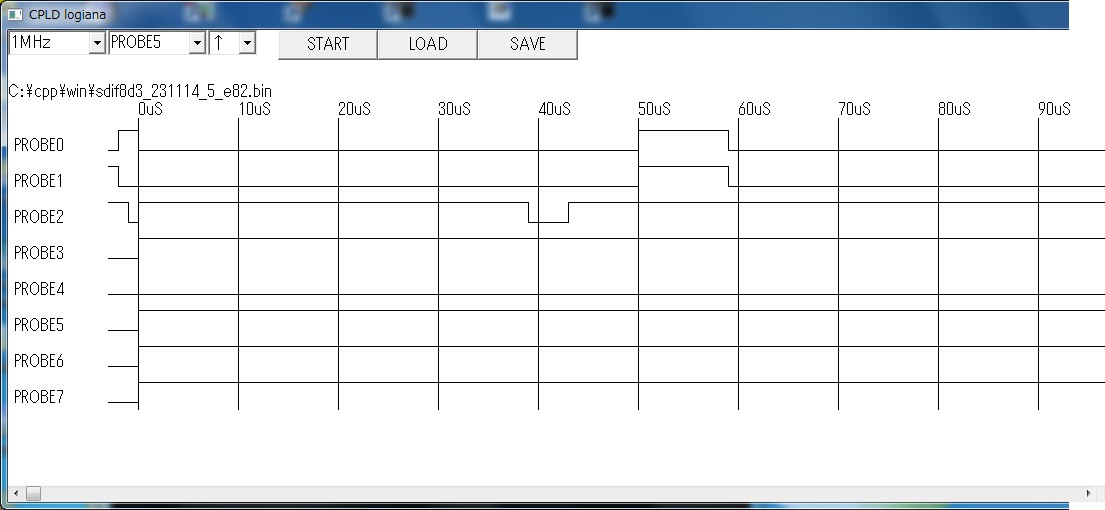

忋婰偺忦審偱僉儍僢僠偟偨奺儔僀儞偺攇宍偱偡丅

俹俼俷俛俤俆傪俉俀俠俆俆偺俹俠俀乮俹俬俠侾俉俥俀俆俆侽偺俵俠俴俼乯偵偮側偓傑偟偨丅

俹俬俠侾俉俥俀俆俆侽偺儕僙僢僩儔僀儞偱偡丅

偦偺儔僀儞偑俫乮仾乯偵側傞偲偒偑僩儕僈偵側偭偰應掕偑奐巒偝傟傑偡丅

夋柺偺忋晹偱僩儕僈忦審偲僒儞僾儕儞僌廃攇悢傪愝掕偟傑偡丅

愭偵俽俿俙俼俿儃僞儞傪墴偟偰偐傜俶俢俉侽倅俁丏俆懁偺僾儘僌儔儉傪幚峴偟傑偡乮俰俹丂俙侽侽侽傪幚峴乯丅

應掕偟偨寢壥偼忋偱悇應偟偨捠傝偩偭偨偺偱偡偑丄攇宍偼巹偺悇應偲偼彮偟堎側偭偰偄傑偟偨乮側傞傎偳偦偆側傞偺偐丅偙傟偼婥偑晅偐側偐偭偨側偁乯丅

俹俼俷俛俤侽乣俹俼俷俛俤俁偼愭傎偳偺恾偲摨偠暲傃偱偡丅

俹俼俷俛俤侽偼俶俢俉侽倅俁丏俆偐傜偺俠俴俲弌椡乮俹俠侾乯偱偡丅

俹俼俷俛俤侾偼俶俢俉侽倅俁丏俆偐傜偺俢俙俿俙弌椡乮俹俠侽乯偱偡丅

俹俼俷俛俤俀偼俹俬俠侾俉俥俀俆俆侽偐傜偺俼俤俙俢倄丵乛俛倀俽倄弌椡乮俼俙俁丄俹俠俈乯偱偡丅

俹俼俷俛俤俁偼俹俬俠侾俉俥俀俆俆侽偐傜偺俢俙俿俙弌椡乮俼俙俀丄俹俠俇乯偱偡丅

俹俬俠侾俉俥俀俆俆侽偺俼俤俽俤俿怣崋乮俹俴俷俛俤俆乯偑俫偵側偭偰偐傜係侽兪倱屻偵俹俼俷俛俤俀偑俴偵側偭偰偄傑偡丅

偙偙偱俿俼俬俽俙偑幚峴偝傟偨偙偲傪帵偟偰偄傑偡丅

俹俼俷俛俤俁偼俫偺傑傑曄壔偟偰偄傑偣傫丅

俹俼俷俛俤俀偼栺係兪倱屻偵俫偵側傝偦偺屻偼偢偭偲俫偺傑傑偺傛偆偵尒偊傑偡丅

偦傟偵偮偄偰偼懕偒偑偁傝傑偡偑丄傑偢偼俹俼俷俛俤侽偲俹俼俷俛俤侾偺攇宍偵偮偄偰愢柧傪偟偰偍偒傑偡丅

俹俼俷俛俤俀偑俴偵側偭偰偐傜俹俼俷俛俤侽丄俹俼俷俛俤侾偑俫偵側傞傑偱偵侾侽兪倱傎偳偐偐偭偰偄傑偡丅

偙傟偼俶俢俉侽倅俁丏俆懁偺僾儘僌儔儉偺抶傟偵傛傞傕偺偱偡丅

壓偼俶俢俉侽倅俁丏俆偺偦偺晹暘偺僾儘僌儔儉偱偡丅