慻傒棫偰僉僢僩傪巊偭偰帺嶌偵挧愴両

乵戞係侽俇夞乶

仠俲俴俆俠俉侽俙侾俀偺夦乮俆乯

慜夞偱堦墳偼廰乆側偑傜堦審棊拝偟偨偺偱偡偑壗偐怱偺墱偱偼偔偡傇偭偰偄傞傕偺偑偁傞傛偆偱丅

擮偺偨傔偵僂儔傪庢偭偰偍偔偙偲偵偟傑偟偨丅

慜夞傑偱偺偲偙傠偱俬俶俿偼俼俙俵偑僙儗僋僩偝傟偰偄偰俵侾偑敪峴偝傟偰偄傞偲偒偲偄偆偺偑忦審偱偡偲偄偆偙偲傪彂偄偰偒傑偟偨丅

偦偺偼偢側偺偱偡偗傟偳擮偺偨傔偵偦偙偺僂儔傪庢偭偰偍偙偆偲偄偆傢偗偱偡丅

偱丅

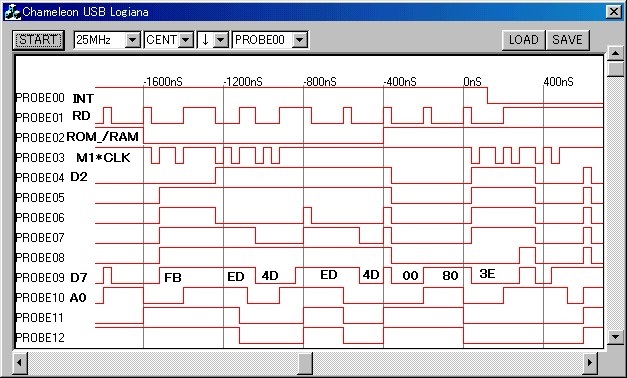

儘僕傾僫偱崱傑偱僨乕僞儔僀儞偵偟偰偄偨偲偙傠偐傜俀杮奜偟偰俼俷俵丵乛俼俙俵僙儗僋僩怣崋偲俵侾怣崋傪娤應偡傞偙偲偵偟傑偟偨丅

俹俼俷俛俤侽俀偑俼俷俵丵乛俼俙俵怣崋偱偡丅

乵戞係侽俀夞乶偺夞楬恾偱俈係俫俠俈係偺倫倝値侾偵擖偭偰偄傞怣崋偱偡丅

偙偺怣崋偑俴偺偲偒乮偮傑傝俼俷俵偑僙儗僋僩偝傟偰偄傞偲偒乯俈係俫俠俈係偺弌椡偼僋儕傾偝傟傞偺偱俻丵弌椡乮俬俶俿乯偼俫偵側傝傑偡丅

俹俼俷俛俤侽俁偼捈愙俵侾偵偮側偖偲傛偄偺偱偡偑偪傚偭偲怣崋偑庢傝偵偔偄偲偙傠偵偁傞偺偱偙傟傕俈係俫俠俈係偺倫倝値俁偵偮側偄偱偄傑偡丅

偙偙偵偼俵侾偲俠俴俲偺俙俶俢偑擖偭偰偄傑偡丅

俵侾丵偲俠俴俲偑偲傕偵俴偺偲偒偵偙偙偑俴偵側傝傑偡丅

倫倝値俁偼俈係俫俠俈係偺俠俴俲擖椡偱俠俴俲偑仾偺偲偒弌椡偑儔僢僠偝傟傑偡丅

俶俢俉侽倅俁丏俆偱偼俵侾丵傪僀儞僶乕僩偟偰擖傟偰偄傑偡偑俶俢俉侽俲俴偺応崌偼俙俵侾俉俉偲夞楬傪寭梡偡傞偨傔偵偙偺夞楬偵偟偰偄傑偡丅

俹俼俷俛俤侽俁偵暆偺偣傑偄僷儖僗偑擖偭偰偄傞偲偒偑俵侾丵偑俴偺偲偒偱偡丅

偙偆偟偰傒傞偲俬俶俿偼妋偐偵俵侾丵偑俴偵側偭偨偲偒偵弌椡偝傟偰偄傑偡丅

偲偙傠偱丅

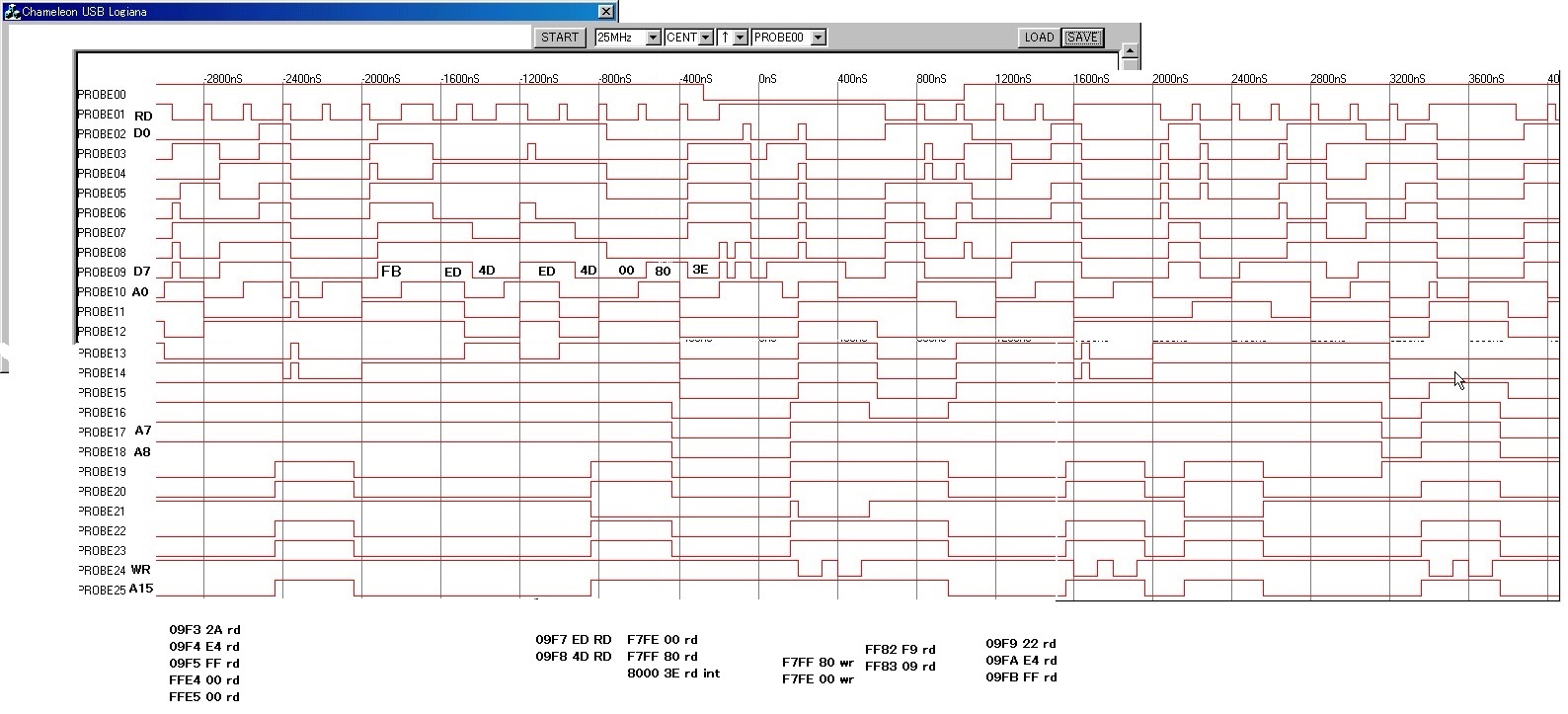

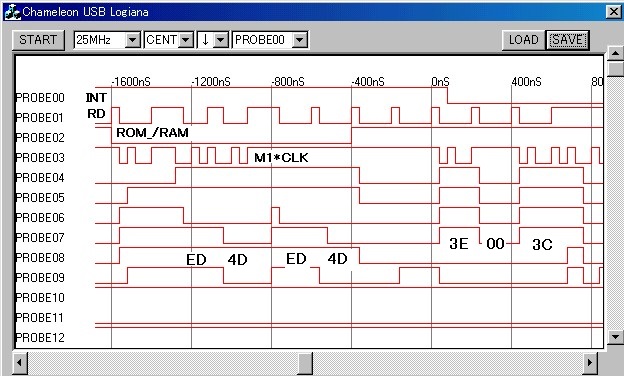

偦傟偱妋擣偟偨偐偭偨偙偲偼妋擣偱偒偨偺偱偡偑偍偐偟側偙偲偵婥偑偮偄偰偟傑偄傑偟偨丅

側傫偲俤俢丂係俢乮俼俤俿俬乯偑俀搙俼俢偝傟偰偄傑偡丅

偙傟偼偍偐偟偄丅

偟偐傕嵟弶偺俼俤俿俬偼俵侾丵偑弌椡偝傟偰偄傑偡偑懕偔俤俢丂係俢偼俵侾丵偑偁傝傑偣傫丅

偳偆傕柦椷僐乕僪偱偼側偔偰僨乕僞偲偟偰撉傫偱偄傞傛偆偱偡丅

側傫偠傖偙傟偼丠

傕偆彮偟偼偭偒傝妋擣偡傞偨傔偵乵戞係侽係夞乶偺儘僕傾僫弌椡恾偵俤俢丂係俢傪彂偒壛偊偰傒傑偟偨丅

傗偭傁傝俀搙撉傒傪偟偰偄傑偡偹偊丅

偙偙偑堎忢摦嶌偵娭學偟偰偄傞偺偐偲巚偭偨偺偱僾儘僌儔儉廋惓屻偺乮惓忢摦嶌偡傞乯俼俷俵偱傕妋偐傔偰傒傑偟偨丅

崱夞偼偦偙偺偲偙傠偑暘偐傟偽傛偄偺偱傾僪儗僗儔僀儞偼偮側偄偱偄傑偣傫丅

傗偭傁傝摨偠偱偟偨丅

偆傓傓傓傓丅

崱崰偵側偭偰偱偡偗傟偳俲俴俆俠俉侽俙侾俀偼偪傚偄偲夦偟偄俠俹倀側偺偐側偁偲巚偭偰偟傑偄傑偡丅

僷僜僐儞傪偮偔傠偆両乵戞係侽俇夞乶

俀侽俀俇丏俀丏俀俇倳倫倢倧倎倓

慜傊

師傊

栚師傊栠傞

儂乕儉儁乕僕僩僢僾傊栠傞