昗弨俿俿俴偩偗乮両乯偱CPU傪偮偔傠偆両乮慻棫偰僉僢僩偱偡両乯

(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞俆侽俋夞乶

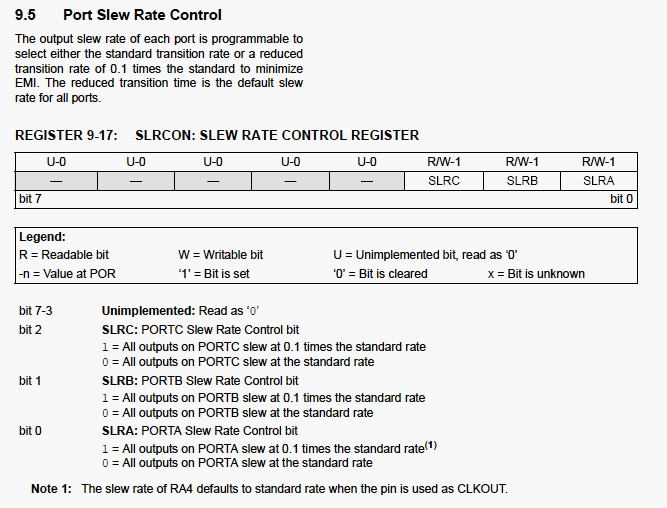

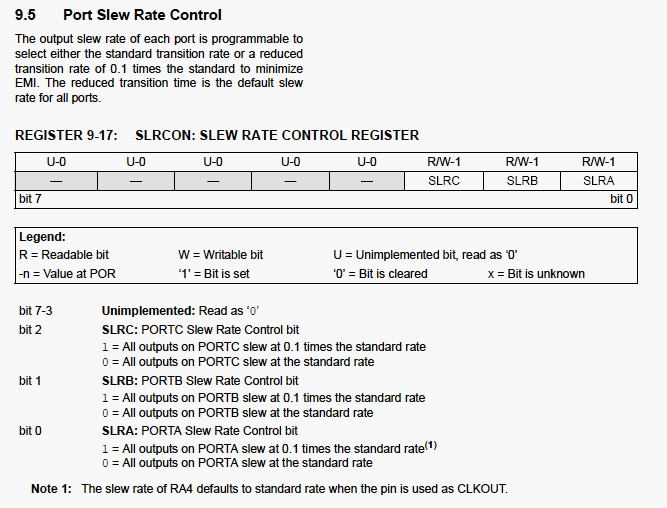

仠俽俴俼俠俷俶儗僕僗僞丠

俹俬俠侾俉俥侾係俲俆侽偺摦嶌僥僗僩傪偡傞偨傔偵丄俹俬俠侾俉俥侾係俲俆侽偺俢倎倲倎俽倛倕倕倲傪撉傫偱偄傑偟偨傜丄尒偨偙偲偺側偄儗僕僗僞偵偮偄偰偺愢柧偵傇偮偐傝傑偟偨丅

側傫偠傖偙傝傖偁丠

乵弌揟乶俵俬俠俼俷俠俫俬俹幮俹俬俠侾俉俥侾倶俲俆侽俢倎倲倎俽倛倕倕倲

偆傓傓丅

俵俬俠俼俷俠俫俬俹偝傫傕傛偔傢偐傜側偄偙偲傪傗偭偰偔傟傑偡丅

側傫偩偐偄傑傂偲偮棟夝偵嬯偟傓偲偙傠側偺偱偡偑丄偳偆傗傜俬乛俷億乕僩偺弌椡偺僗儖乕儗乕僩傪壛尭偡傞丄偲偄偆偙偲偺傛偆偱偡丅

僗儖乕儗乕僩丠

偼偰丠

側傫偱傑偨偦傫側偙偲傪丠

傛偔偼傢偐傜側偄偺偱偁傝傑偡偑丅

偟偐傕丄僨僼僅儖僩偱偼僗僞儞僟乕僪偱偼側偄愝掕偵側傞偺偩偲偐丅

倎倲丂侽丏侾倲倝倣倕倱偲偁傝傑偡偐傜丄倲倰倎値倱倝倲倝倧値丂倰倎倲倕偮傑傝棫偪忋偑傝棫偪壓傝偺懍偝偲偄偆偙偲偱偟傚偆偐丄偦傟偑侽丏侾倲倝倣倕倱偮偆偺偼悢抣偩偗傪尒傞偲傔偪傖傔偪傖懍偔側傞丄傛偆偵巚偭偰偟傑偆偐傕偟傟傑偣傫偑乧丅

偦傟偼懡暘倲倝倣倕倱傪僞僀儉偡側傢偪帪娫偲偲傜偊傞偲偦偺傛偆偵報徾偟偰偟傑偄傑偡丅

偟偐偟倲倝倣倕偱偼側偔偰倲倝倣倕倱側偺偱偡傛偹偊丅

倲倝倣倕倱偲偄偆応崌偵偼丄妋偐丄仜攞偲偄偆堄枴偩偭偨偲婰壇偟偰偍傝傑偡偑乧丅

偦偆偩偲偡傞偲丄侽丏侾倲倝倣倕倱偼侽丏侾攞偲偄偆偙偲偱偡偐傜丄傔偪傖傔偪傖抶偔側偭偰偟傑偄傑偡丅

傑偁側偵傪婎弨偵偟偰丄偦偺侽丏侾攞偐丄偲偄偆偲偙傠偑傛偔偼傢偐傜側偄偺偱偡偑丅

偦傟偵偟偰傕丄傕偟傕侽丏侾倲倝倣倕倱偑偦偆偄偆堄枴偩偲偟偨傜丄側偤傢偞傢偞抶偔偟側偗傟偽側傜側偄偺偐丅

偆傓傓丅

側偧偱偡偹偊丅

側偵偼偲傕偁傟丄帋偟偰傒傞偙偲偑堦斣偺嬤摴偱偡丅

慜夞偺僾儘僌儔儉偵俽俴俼俠俷俶偺偲偙傠偩偗捛壛偟傑偟偨丅

;;;pic p18f14k50 test program

;f14k50test3

;10/5/21

;

;

#include<p18f14k50.inc>

;cpuclock=32MHz internal oscillator

;

CONFIG FOSC = IRCCLKOUT,WDTEN=OFF,LVP=OFF;not WDT

;

org 00

movlw 64;clock=8MHz,select Primary Clock

movwf OSCCON

movlw 40;PLL on for intosc=8MHz only

movwf OSCTUNE

clrf ANSEL;PORTA,PORTC are digital

clrf ANSELH;PORTB,PORTC are digital

clrf SLRCON

clrf TRISA;porta=out

clrf TRISB;portb=out

clrf TRISC;portc=out

;

movlw 1

loop

xorwf PORTC

goto loop

;

end

僨僼僅儖僩偱偼俽俴俼俠俷俶偺倐倝倲侽乣倐倝倲俀偼侾偵側傞傛偆偱偡丅

偲偄偆偙偲偼僗僞儞僟乕僪儗乕僩偱偼側偔偰丄偦偺侽丏侾倲倝倣倕倱偵側偭偰偄傞偙偲偵側傝傑偡丅

偦偙偱僾儘僌儔儉偱俽俴俼俠俷俶偺慡價僢僩傪侽偵偟傑偟偨丅

們倢倰倖丂俽俴俼俠俷俶偱偡丅

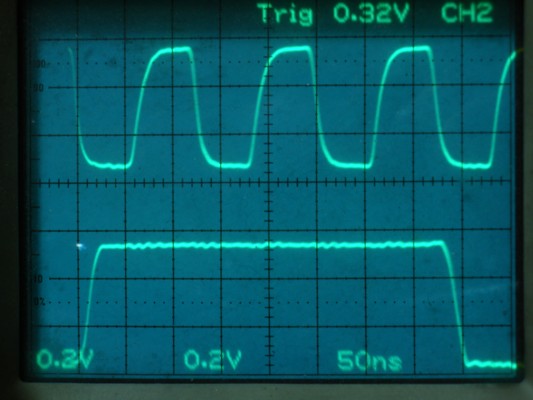

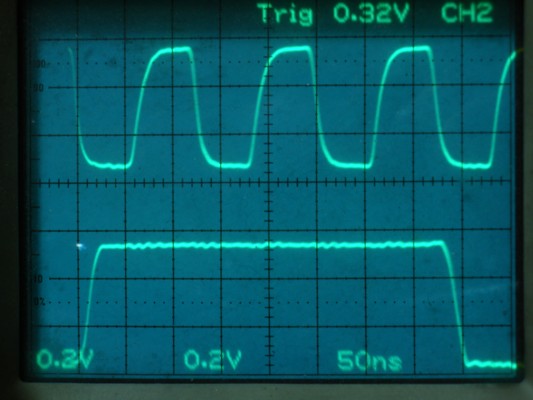

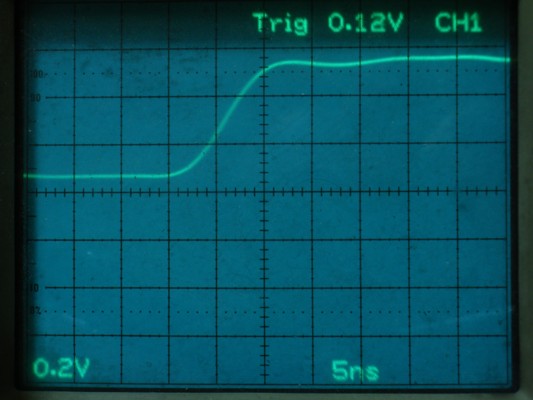

仠僾儘僌儔儉俿俤俽俿俁偺弌椡攇宍偱偡

僾儘僌儔儉傪幚峴拞偺俼俠侽偐傜偺弌椡攇宍偱偡丅

壓懁乮俠俫俀乯偑俼俠侽偐傜偺弌椡偱偡丅

俽俴俼俠俷俶亖侽偵偟傑偟偨偐傜丄僗儖乕儗乕僩偼僗僞儞僟乕僪偱偡丅

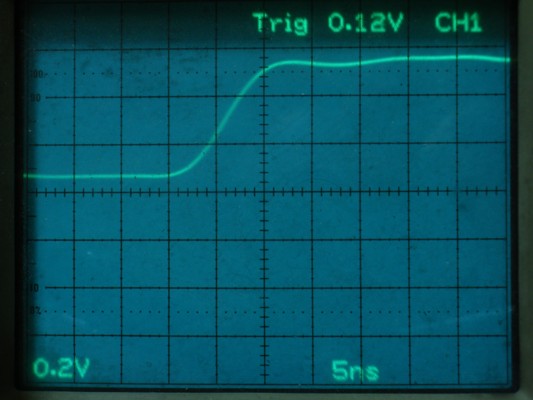

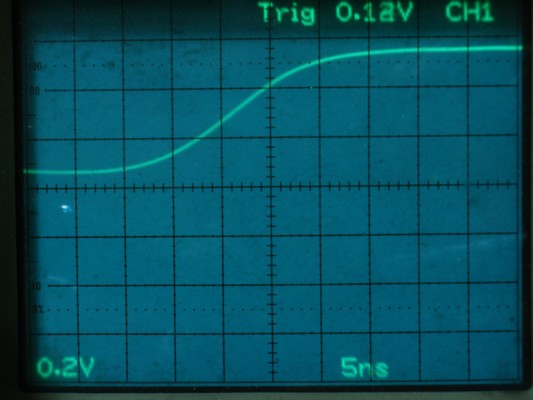

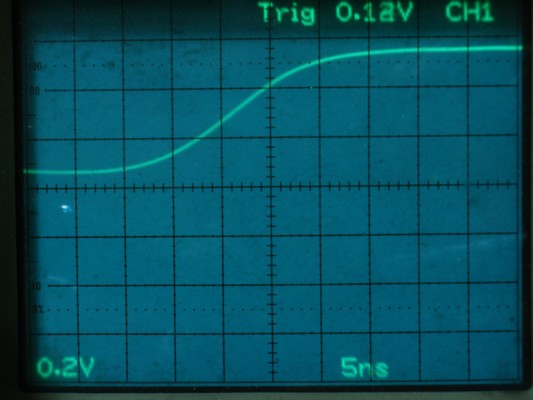

偙傟傪慜夞偺俿俤俽俿俀偺弌椡攇宍偲斾傋偰傒傑偟傚偆丅

慜夞偺僾儘僌儔儉俿俤俽俿俀偱偼俽俴俼俠俷俶偼偝傢偭偰偄傑偣傫偐傜丄僨僼僅儖僩偺愝掕丄偮傑傝僗僞儞僟乕僪偺侽丏侾倲倝倣倕倱偺僗儖乕儗乕僩偱偡丅

偦偆偄偊偽側傫偩偐偙偪傜偺傎偆偑丄岡攝偑備傞傗偐側傛偆側乧丅

俠俫俀偺攇宍傪奼戝偟偰斾傋偰傒傑偟傚偆丅

傑偢丄偙偪傜偼崱夞偺俿俤俽俿俁偺攇宍偱偡丅

偦偟偰偙偪傜偑慜夞偺俿俤俽俿俀偺攇宍偱偡丅

偨偟偐偵丄偙偪傜乮侽丏侾倲倝倣倕倱乯偺傎偆偑備傞傗偐側傛偆偱偡丅

偱傕丄偙傫側傕偺偑側偤昁梫側偺偱偟傚偆偐偹偊丅

俀侽侾侽丏俆丏俀俇倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞