トランジスタで8080をつくってしまおうというまさにびっくり仰天、狂気のプロジェクトです!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

見事にできましたら、もちろんTK−80モニタを乗せて、それからBASIC、CP/Mを走らせましょう!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

[第374回]

●クロックエッジの検出(2)

前回からの続きです。

前回の終わりのところで、クロックエッジで幅の狭いパルスを出力する回路として下の回路図をお見せしました。

回路の動作を理解しやすくするために実際の回路からPC0のCKdn回路のみを取り出しました。

前回も書きましたが回路の動作としては信号の「立ち上がり」のときにパルスが出力される回路になっているためにMCLKをインバータで反転させた信号を回路の入力信号にしています。

上の回路にMCLKが入力され、それがCKdnL信号として[5]のNANDゲートから出力されるまでの各部の波形を下に図示します。

[1]の出力は抵抗Rを通してコンデンサCを充放電するため[2]の入力点の波形は図のようになります。

約1/2Vccが[2]のインバータのスレッショルド電圧となるため[2]の出力は反転するとともに[1]の出力からわずかに遅延します。

[3]、[4]のインバータは波形整形のために入れています。

なお各インバータそのものの遅延時間は思ったよりも短くて10ns以下のレベルです。

なのでRCを通さずインバータのみでは十分な遅延効果が得られないことを確認済みです。

そのわずかな遅延も含めて[2]の出力は[4]のインバータの出力となり、それは[5]のNANDゲートの一方の入力となります。

[5]のNANDゲートのもう一方の入力には遅延回路を通す前の[1]の出力信号が入力されます。

すると図のように遅延したわずかな時間だけ2つの入力がともにHになるためその期間だけ[5]から幅の狭いパルスが出力されます。

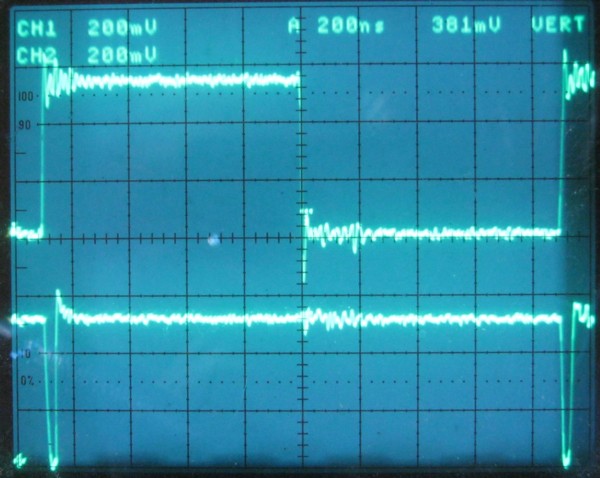

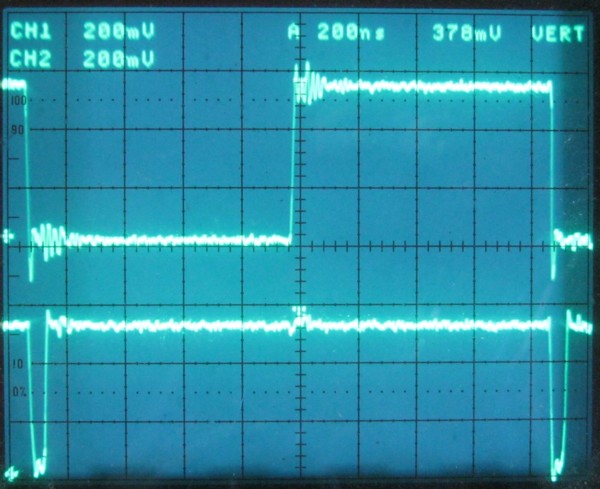

上の回路の波形をオシロスコープで確認しました。

CH1(上側)が[1]の出力波形でCH2(下側)は[5]の出力波形です。

CH1の立ち上がりのときにCH2に幅の狭いパルスが観測されています。

CH1の波形から見れば立ち上がりエッジですが上のほうでも書きました通り[1]の出力はMCLKをインバータによって反転したものなのでPC(プログラムカウンタ)回路としてはMCLKの立ち下がりエッジでの出力(CKdnL)です。

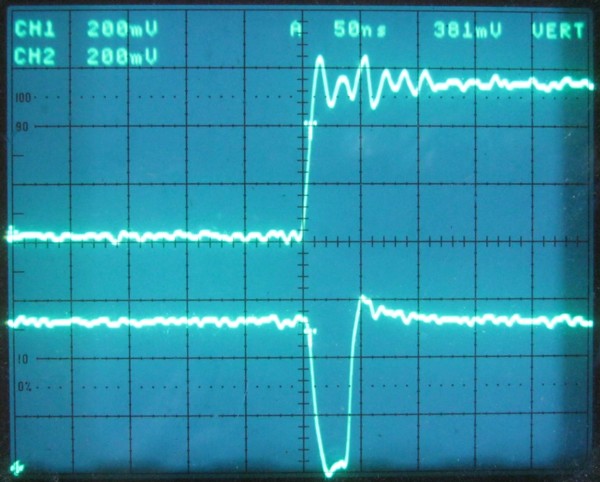

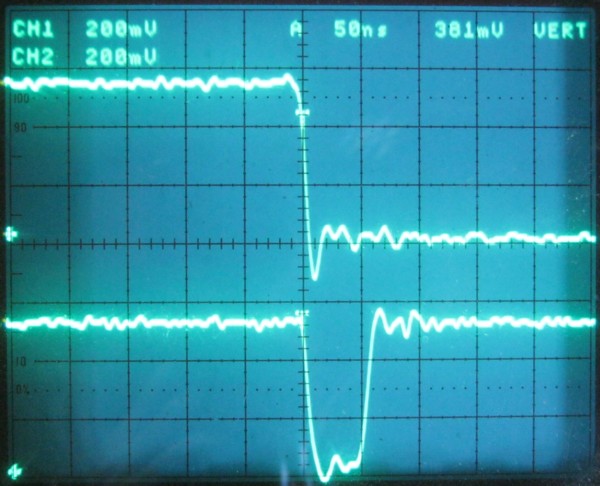

時間軸を拡大しました。

CH2のパルス幅は50nsほどです。

実は抵抗Rは1KΩなのですがコンデンサCとしては何も実装していません。

1KΩ抵抗だけでこれだけの遅延を得ています。

それならインバータ3段の遅延なのでは?という疑問が出てきますがこれも上に書きました通りインバータだけではほとんど遅延しないため十分な幅の出力パルスが得られません。

当初R=1KΩ、C=100pFでテストしてみましたがそのときは出力パルス幅は約100nsでした。

100nsでもよいのではと考えていたのですがテストを進めるうちにそれでは幅が大きすぎて問題が出てくることがわかりましたので、色々試した結果R=1KΩでCは実装しないというところに落ち着きました。

やはりここはできるだけ幅が狭いパルスであることが望ましいのですが余り幅が狭いとパルスがつぶれてしまう危険があることのほか、本来の目的であるプログラムカウンタに十分なラッチがかからない可能性が出てきます。

とりあえずこのくらいのパルス幅が問題がないところなのではないかと考えています。

上の回路図では省いた立ち上がりエッジでの出力波形についてもオシロスコープで観測してみました。

CH1が[1]の出力波形でCH2は回路図では省略したCKupL信号の波形です。

CH1の立ち下がりのときにCH2のパルスが出力されていますから立ち下がりエッジのときの出力に見えますが、上でも書きました通り、[1]はMCLKをインバータで反転した波形なので、PC(プログラムカウンタ)の動作としてはMCLKの立ち上がりエッジでのパルス出力ということになります。

時間軸を拡大しました。

こちらもパルス幅は50nsほどです。

トランジスタでCPUをつくろう![第374回]

2021.7.11upload

前へ

次へ

ホームページトップへ戻る