僩儔儞僕僗僞偱俉侽俉侽傪偮偔偭偰偟傑偍偆偲偄偆傑偝偵傃偭偔傝嬄揤丄嫸婥偺僾儘僕僃僋僩偱偡両

仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚

尒帠偵偱偒傑偟偨傜丄傕偪傠傫俿俲亅俉侽儌僯僞傪忔偣偰丄偦傟偐傜俛俙俽俬俠丄俠俹乛俵傪憱傜偣傑偟傚偆両

仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚

乵戞俀侽係夞乶

仠俷俹僐乕僪僼僃僢僠夞楬乮係乯摦嶌僥僗僩

崱夞偼俷俹僐乕僪僼僃僢僠夞楬帋嶌婎斅偺摦嶌僥僗僩偱偡丅

僥僗僩偼俶俢俉侽倅俁丏俆偺俉俀俠俆俆擖弌椡僐僱僋僞偵乵戞侾俋俆夞乶偱嶌偭偨僼儔僢僩働乕僽儖傪愙懕偟偰丄俛俙俽俬俠僾儘僌儔儉偱峴側偄傑偡丅

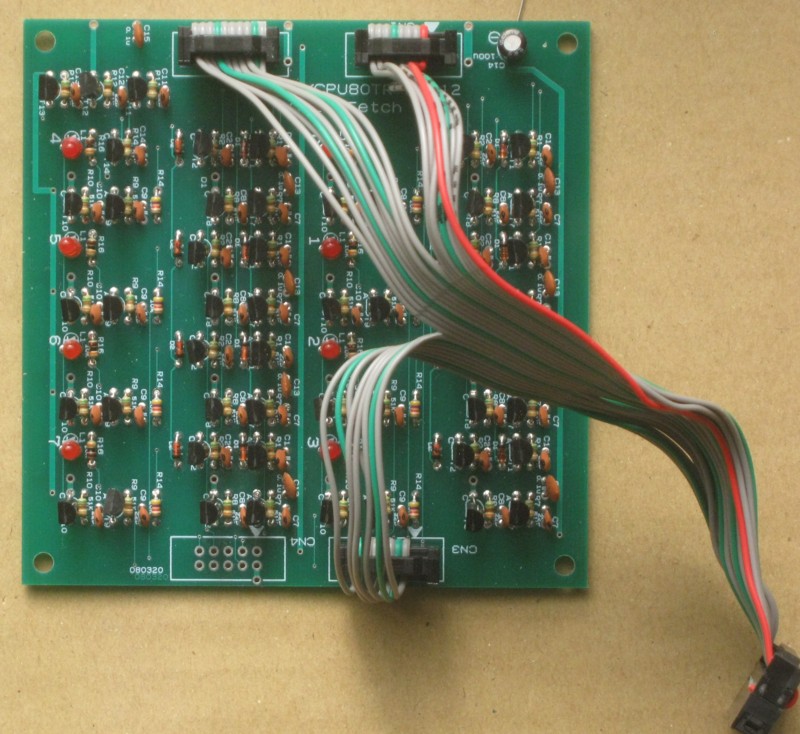

壓偼俷俹僐乕僪僼僃僢僠夞楬帋嶌婎斅偵僼儔僢僩働乕僽儖僐僱僋僞傪愙懕偟偨幨恀偱偡丅

幨恀偱偼僐僱僋僞偺岦偒偑埆偔偰偪傚偭偲尒偵偔偄偱偡偑丄働乕僽儖偺斀懳懁偼俀俇倫倝値僐僱僋僞偵側偭偰偄傑偡丅

偦偪傜傪俶俢俉侽倅俁丏俆偺俉俀俠俆俆擖弌椡梡僐僱僋僞偵愙懕偟傑偡丅

僐僱僋僞偺寢慄偼乵戞侾俋俆夞乶偺愙懕恾偲摨偠偱偡偑丄帋嶌婎斅懁偺怣崋偼堎側傝傑偡丅

俉俀俠俆俆偺俹俙侽乣俹俙俈偺弌椡傪帋嶌婎斅偺俢侽乣俢俈偵偮側偓傑偡丅

僨乕僞偺儔僢僠怣崋偼杮棃偼俠俹倀僋儘僢僋偺俿侾偱偡偑丄崱偼摦嶌僥僗僩偱偡偐傜俿侾偺戙傢傝偵俹俠俈傪偮側偓傑偡丅

帋嶌婎斅偐傜儔僢僠弌椡偝傟傞俷俹僐乕僪乮俷俹侽乣俷俹俈乯傪妋擣偡傞偨傔偵俹俛侽乣俹俛俈偺擖椡傪偮側偓傑偡丅

俢侽乣俢俈偲俹俙侽乣俹俙俈偺價僢僩偺暲傃偼堦抳偟偰偄傑偣傫偑丄摦嶌僥僗僩偱偡偐傜寢壥偑惓偟偔妋擣偱偒傟偽傛偄偺偱偦偺傑傑偺愙懕偵偟傑偡丅

偮傑傝俢侽偲俹俙俆丄俢侾偲俹俙係偲偄偆傛偆偵愙懕偡傞偙偲偵側傝傑偡丅

摨條偺偙偲偼俷俹侽乣俷俹俈偲俹俛侽乣俹俛俈偵傕偁偰偼傑傝傑偡丅

偙偪傜傕暲傃偼堎側傝傑偡偑偙偺傑傑愙懕偟傑偡丅

俷俹侽偲俹俛俇丄俷俹侾偲俹俛俈偲偄偆傛偆偵愙懕偡傞偙偲偵側傝傑偡丅

堦尒偡傞偲偦偺傑傑偱偼僥僗僩寢壥偺擖椡偲弌椡偺暲傃偑偱偨傜傔偵側偭偰偟傑偭偰丄寢壥偺妋擣偑偟偵偔偄傛偆偵巚傢傟傑偡偑丄岾偄擖椡偲弌椡偺娫偵偼婯懃惈偑偁傝傑偡丅

帋嶌婎斅偺懁偺俢侽乣俢俈偲俷俹侽乣俷俹俈偼摨偠暲傃偱偡丅

堦曽偱俉俀俠俆俆偺僐僱僋僞偺俹俙侽乣俹俙俈偲俹俛侽乣俹俛俈傪尒偰傒傞偲丄俹俙侽乣俹俙俁偲俹俛侽乣俹俛俁偼摨偠暲傃偵側偭偰偄傑偡丅

傑偨俹俙係乣俹俙俈偲俹俛係乣俹俛俈偼挌搙弴彉偑媡偵側偭偰偄傑偡丅

偙偺偙偲偐傜僾儘僌儔儉偱俹俙侽乣俹俙俈偵摿暿偺壛岺傪偟側偄偱晛捠偵僨乕僞傪弌椡偟偰丄偦偺寢壥傪帋嶌婎斅傪捠偟偰俹俛侽乣俹俛俈偱庴偗傟偽丄偦偺寢壥偑惓偟偄偐偳偆偐偼廫暘敾抐偱偒傑偡丅

壓偼崱夞僥僗僩偺偨傔偵嶌偭偨俛俙俽俬俠僾儘僌儔儉偱偡丅