(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞係俁俈夞乶

仠俵倄俠俹倀俉侽偺偛拲暥傪偄偨偩偒傑偟偨

墶昹巗偺俰俫條偐傜丄俵倄俠俹倀俉侽慻棫僉僢僩傪俀僙僢僩丄偛拲暥偄偨偩偒傑偟偨丅

俰俫條丅偛拲暥桳擄偆偛偞偄傑偟偨丅

僾儕儞僩婎斅傪敪拲偄偨偟傑偟偨丅

婎斅偑弌棃偁偑偭偰偒傑偡傑偱丄偟偽傜偔偍懸偪偔偩偝偄傑偡傛偆偍婅偄偄偨偟傑偡丅

仠僗僥僢僾夞楬

崱夞傕倅俉侽斉俿俲俉侽夞楬偺偍榖偱偡丅

俿俲俉侽偲俵倄俠俹倀俉侽乮俿俲俉侽夞楬乯偺丄僗僥僢僾夞楬丄僗僥僢僾摦嶌偺巇慻傒偵偮偄偰偼丄乵戞俀係侾夞乶偐傜壗夞偐偵傢偨偭偰愢柧傪偟傑偟偨丅

俿俲俉侽傕俵倄俠俹倀俉侽乮俿俲俉侽夞楬乯傕丄僗僥僢僾摦嶌偼妱傝崬傒傪棙梡偟偰偄傑偡丅

俉侽俉侽偼俤俬柦椷偲俢俬柦椷偵傛偭偰丄妱傝崬傒傪庴偗晅偗壜擻偵偡傞乮俤値倎倐倢倕丂俬値倲倕倰倰倳倫倲乯偐丄妱傝崬傒傪庴偗晅偗偱偒側偄傛偆偵偡傞乮俢倝倱倎倐倢倕丂俬値倲倕倰倰倳倫倲乯偐傪僾儘僌儔儉偱僐儞僩儘乕儖偡傞偙偲偑偱偒傑偟偨丅

儅僗僇僽儖僀儞僞儔僾僩乮俵倎倱倠倎倐倢倕丂俬値倲倕倰倰倳倫倲乯偱偡丅

崱夞偺倅俉侽斉俿俲俉侽傕丄僗僥僢僾摦嶌偵偼丄儅僗僇僽儖僀儞僞儔僾僩乮俬俶俿乯傪棙梡偟偰偄傑偡丅

俉侽俉侽偺妱傝崬傒偼俬俶俿怣崋擖椡偵傛偭偰峴傢傟傞儅僗僋壜擻側妱傝崬傒偩偗偩偭偨偺偱偡偑丄倅俉侽偱偼偦偺傎偐偵儅僗僋偱偒側偄妱傝崬傒乮俶俵俬乯偑偁傝傑偡丅

傑偨儅僗僋壜擻側妱傝崬傒傕丄俉侽俉侽偲摨偠儌乕僪偺傎偐偵傕梡堄偝傟偰偄傑偡丅

仠俶俵俬

倅俉侽斉俿俲俉侽傕俿俲俉侽偲摨偠傛偆偵丄僗僥僢僾摦嶌偱偼儅僗僋壜擻側妱傝崬傒乮俬俶俿乯傪巊偄傑偡偐傜丄崱夞偺偍榖偲偟偰偼俶俵俬偼娭學偁傝傑偣傫丅

偱偡偗傟偳丄偣偭偐偔俶俵俬偲偄偆尵梩偑偱偰偒偨偺偱偡偐傜丄偲傝偁偊偢偼丄傑偢倅俉侽偺俶俵俬偲偄偆傕偺偵偮偄偰丄娙扨偵愢柧傪偡傞偙偲偵偄偨偟傑偡丅

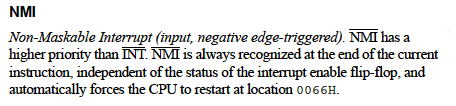

俶俵俬偼俬俶俿偲堘偭偰丄妱傝崬傒偺嫋壜丄晄嫋壜傪僜僼僩僂僃傾偱僐儞僩儘乕儖偡傞偙偲偑偱偒傑偣傫丅

偳傫側応崌乮偨偲偊偽俠俹倀偑朶憱偟偨傛偆側偲偒偲偐僴儞僌傾僢僾偟偰偟傑偭偨偲偒側偳乯偱傕丄俶俵俬偼昁偢庴偗晅偗傜傟傑偡丅

偦偆偄偆偲偒偺偨傔偵偼丄俼俤俽俤俿抂巕偑偁傞傢偗偱偡偑丄儕僙僢僩傪偡傞偲弶婜忬懺偵栠偭偰偟傑偆偨傔丄揹尮搳擖帪偲摨偠張棟偐傜奐巒偡傞偙偲偵側偭偰偟傑偄傑偡丅

偦偙傑偱偼偟偨偔側偄偑丄僴儞僌傾僢僾忬懺偼僋儕傾偟偨偄丄偲偄偆傛偆側偲偒偺偨傔偵俶俵俬偑梡堄偝傟偰偄傑偡丅

偲巚偭偰偄偨偺偱偡偑丄偦傕偦傕偺栚揑偼偦偆偄偆偨傔偺傕偺偱偼側偐偭偨傛偆偱偡乮屻弎乯丅

倂倝値倓倧倵倱僷僜僐儞偺儕僙僢僩儃僞儞偑俠俹倀偺俼俤俽俤俿偵憡摉偡傞偲偡傟偽丄乵俙倢倲乶乵俠倲倰倢乶乵俢倕倢倕倲倕乶偺擖椡偑俶俵俬偲偄偆偙偲偵側傝傑偡丅

嬞媫帪妱傝崬傒丄僗乕僷乕僶僀僓乕僐乕儖傪壜擻偵偟傑偡丅

俶俵俬妱傝崬傒偼倅俉侽俠俹倀偺俶俵俬抂巕傪俴偵偡傞偙偲偱庴偗晅偗傜傟傑偡丅

俶俵俬怣崋偑擖椡偝傟傞偲丄俠俹倀偼柍忦審偱丄傾僪儗僗侽侽俇俇斣抧偐傜偺僾儘僌儔儉傪幚峴偟傑偡丅

偲偙傠偱丅

撍慠側偺偱偡偑丄乵戞係俁俆夞乶偱偛徯夘偟偨倅俉侽偺乽俢倎倓倎倱倛倕倕倲乿側偺偱偡偑丄偄偔傜側傫偱傕娙扨偡偓偰丄偙傟偠傖偁徻嵶偵偮偄偰偼傢偐傝傑偣傫丅

偙傟偼乽俢倎倲倎倱倛倕倕倲乿偲偄偆傛傝傕丄僷儞僼儗僢僩傒偨偄側傕偺偱偡丅

偍傑偗偵暥帤傕恾斉傕撉傒偵偔偔偰丄偄偐偵傕暋幨偲偄偭偨姶偠偱偡丅

傕偆偪偭偲乽傑偟乿側傕偺偼柍偄偺偐丄偲偄偆偙偲偱偁傜偨傔偰憑偟偰傒傑偟偨丅

偦偟偨傜丄傗偭傁傝偁傝傑偟偨丅

仠倅俉侽丂倀倱倕倰丂俵倎値倳倎倢

俁侽俉儁乕僕偁傝傑偡丅

偦偆偱偟傚偆丅偦偆偱偟傚偆丅傗偭傁傝偙偺偔傜偄偼梸偟偄偱偡偹偉丅

偲偙傠偱丄偙偺俵俙俶倀俙俴側偺偱偡偑丄巹偺憑偟曽偑埆偐偭偨偺偐丄倅倝倢倧倗幮偺僒僀僩撪専嶕偱偼弌偰偒傑偣傫偱偟偨丅

偆偆丅

偱傕丄傑偁丄傛偦條偺偙偲偵梋傝暥嬪傪尵偊偨傕偺偱偼側偄偺偱偡偹偊丅

僂僠乮拞擔揹岺乯偺僒僀僩偩偭偰丄憡摉偵偄偄壛尭側偮偔傝偱丄帺暘偱傕丄偳偙偵壗偑抲偄偰偁傞偺偐丄傢偐傜側偄忬嫷偱偡偐傜乧丅

嵟嬤偼丄帺暘偑彂偄偨夁嫀婰帠傪専嶕偡傞偺偵丄傕偭傁傜俧倧倧倗倢倕條乮幚嵺偼姷傟偰偄傞偺偱俧倧倧専嶕乯偺偍悽榖偵側偭偰偍傝傑偡乧乮娋乯丅

俧倧倧倗倢倕偱丄乽倸倝倢倧倗丂倸俉侽丂倳倱倕倰丂倣倎値倳倎倢乿偱専嶕偡傞偲丄専嶕僩僢僾偵昞帵偝傟傑偡丅

偊乧丄偲乧丅

偦偆偱偟偨丅俶俵俬偱偟偨丅

偱丄偙偺倅俉侽丂倀倱倕倰丂俵倎値倳倎倢傪尒偰傒傑偡偲丄偙傫側傆偆偵彂偄偰偁傝傑偡丅

乵弌揟乶倅倝倢倧倗幮倅俉侽俠俹倀丂倀倱倕倰乫倱丂俵倎値倳倎倢

偍偍丅偙傟側傜偽丅

偒傟偄側俵俙俶倀俙俴偱偡丅

偱傕乧丅

偒傟偄側偙偲偼傛偄偺偱偡偗傟偳偹偊丅

偙傟偩偗偱偼抦傝偨偄偙偲偑傢偐傝傑偣偸丅

偍傑偗偵俥倝倗倳倰倕侾侽偼丄娞怱偺俶俵俬僷儖僗偑敳偗棊偪偰乮両乯偍傝傑偟偨偺偱丄巹偑昤偒壛偊偰偍偒傑偟偨丅

偍偍丅偦偆偱偡偐丅

乧倲倧丂倫倰倧倴倝倓倕丂倝倣倣倕倓倝倎倲倕丂倰倕倱倫倧値倱倕丂倲倧丂倝倣倫倧倰倲倎値倲丂倱倝倗値倎倢倱丂倱倳們倛丂倎倱丂倎値丂倝倣倫倕値倓倝値倗丂倫倧倵倕倰丂倖倎倝倢倳倰倕丏

側傞傎偳丅

捈栿偟傑偡偲丄

嵎偟敆偭偨乮倝倣倫倕値倓倝値倗乯揹尮堎忢側偳偺廳梫側僔僌僫儖偵偡偽傗偔懳墳偡傞偨傔偵乧丄

俶俵俬偑巊傢傟傞丄偲彂偄偰偁傝傑偡丅

偦偆偱偡偐丅傕偲傕偲偼偦偆偄偆偨傔偵梡堄偝傟偨傕偺偩偭偨偺偱偡偹丅

巹偼偰偭偒傝傕偭傁傜僗乕僷乕僶僀僓乕僐乕儖偑栚揑偩偲巚偄崬傫偱偄傑偟偨丅

傑丅偦傟偼偦傟偱傛偄偺偱偡偗傟偳丅

偱傕丅

偪傚偭偲懸偭偰偔偩偝偄偹乕丅

偙傟傪撉傒傑偡偲丄偱偡偹偊丅

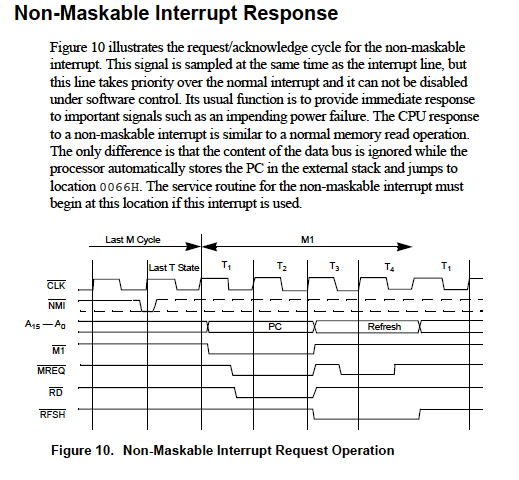

俶俵俬偵懳偡傞丄俠俹倀偺摦嶌偼丄捠忢偺俵倕倣倧倰倷丂俼倕倎倓偲摨偠摦嶌傪偡傞乮丠乯偑丄偟偐偟丄偨偩傂偲偮堎側偭偰偄傞偺偼丄僶僗忋偺僨乕僞偼柍帇偝傟偰丄俹俠乮僾儘僌儔儉僇僂儞僞乯偺抣傪奜晹僗僞僢僋偵僆乕僩儅僠僢僋偵戅旔偟偨偁偲丄侽侽俇俇偵僕儍儞僾偡傞偙偲偱偁傞丅

偙傟偼擔杮岅偵栿偟偰傒偰傕丄偪傚偭偲傛偔傢偐傜側偄暥復偱偡丅

偟偐傕僞僀儈儞僌僠儍乕僩偑傑偨傛偔傢偐傝傑偣傫丅

暥復偐傜偡傞偲丄俶俵俬偑庴偗晅偗傜傟偨偁偲偺丄俵侾偵偁傞俹俠偲偄偆偺偼丄俶倕倶倲丂俬値倱倲倰倳們倲倝倧値偺傾僪儗僗偲偄偆偙偲傜偟偄偺偱偡偗傟偳丄偦偙偐傜愭偵偳偆側傞偺偐偑慡偔傢偐傝傑偣傫丅

偙傟偵偮偄偰偼丄偨傑偨傑庤尦偵僔儍乕僾噴偺倅俉侽僥僋僯僇儖儅僯儏傾儖偑偁傝傑偟偨偺偱丄偦傟傪尒偰傒偨偺偱偡偑丄慡偔摨偠撪梕偱偟偨丅

偦傟偲傕偆傂偲偮丄忋偺暥復偱偼丄俶俵俬偑庴偗晅偗傜傟傞僞僀儈儞僌偵偮偄偰偼丄慡偔彂偐傟偰偄傑偣傫丅

乽捠忢偺倝値倲倕倰倰倳倫倲偲摨偠乿偩側傫偰丄偦傟偼丄庤敳偒偱偟傚偆傛丅

傫偠傖丄偲偄偆偙偲偱丄捠忢偺倝値倲倕倰倰倳倫倲偵偮偄偰尒偰傒傑偟偨傜丄

乵弌揟乶倅倝倢倧倗幮倅俉侽俠俹倀丂倀倱倕倰乫倱丂俵倎値倳倎倢

側傞傎偳丄偙偙偵偼偪傖傫偲彂偄偰偁傝傑偟偨丅

偲偄偆偙偲偼丄俬俶俿傕俶俵俬傕奺柦椷偺嵟屻偺僋儘僢僋偺忋偑傝僄僢僕偱専弌偝傟傞丄偲偄偆偙偲偱偡偹丅

偲偙傠偱丄偙偙偱慺杙側媈栤偱偡丅

俬俶俿偼俤俬丄俢俬偵傛偭偰惂屼偱偒傑偡丅

偱傕丄俶俵俬偼僜僼僩僂僃傾偱偼嬛巭偡傞偙偲偑偱偒傑偣傫丅

偦偆彂偄偰偁傝傑偡偟丄側傫偨偭偰丄俶倧値丂俵倎倱倠倎倐倢倕丂俬値倲倕倰倰倳倫倲側偺偱偡偐傜丄怣崋偑擖偭偨傜丄昁偢丄捈偪偵丄侽侽俇俇偵僕儍儞僾偟偰偟傑偄傑偡丅

偡傞偲乧丅

傕偟傕丄侽侽俇俇偵僕儍儞僾偟偰俶俵俬張棟儖乕僠儞傪幚峴偟偰偄傞偲偒偵傕丄傑偩俶俵俬怣崋偑傾僋僥傿僽偺傑傑偩偭偨傜乧丅

搒崌偑埆偄偺偱偼偁傝傑偣傫偐丠

偦偺媈栤偵懳偟偰偼丄倅俉侽偺抂巕愢柧偺偲偙傠偵彂偄偰偁傝傑偟偨丅

乵弌揟乶倅倝倢倧倗幮倅俉侽俠俹倀丂倀倱倕倰乫倱丂俵倎値倳倎倢

値倕倗倎倲倝倴倕丂倕倓倗倕亅倲倰倝倗倗倕倰倕倓偲彂偄偰偁傝傑偡丅

偪側傒偵丄俬俶俿偺傎偆偼丄偙偺傛偆偵彂偄偰偁傝傑偡丅

乵弌揟乶倅倝倢倧倗幮倅俉侽俠俹倀丂倀倱倕倰乫倱丂俵倎値倳倎倢

俬俶俿偺傎偆偼丄倎們倲倝倴倕丂俴倧倵偱偡偐傜丄俴倧倵儗儀儖偺擖椡怣崋偱偡丅

偦偺俴倧倵儗儀儖偑柦椷偺嵟屻偺僋儘僢僋偺忋偑傝僄僢僕偱専弌偝傟傞丄偲偄偆偙偲偱偡偐傜丄偙偙偼慺捈偵擺摼丄偱偡丅

俬俶俿妱傝崬傒偼丄庴偗晅偗傜傟傞偲丄帺摦揑偵妱傝崬傒嬛巭忬懺偵側傝傑偡偐傜丄俴倧倵儗儀儖偺傑傑偱偁偭偰傕丄廳偹偰妱傝崬傒偑庴偗晅偗傜傟傞偙偲偼偁傝傑偣傫丅

傕偪傠傫妱傝崬傒張棟偑廔傢偭偰丄俤俬柦椷偑幚峴偝傟傞傑偱偺娫偵偼丄俫倝倗倛偵栠偟偰偍偔昁梫偑偁傝傑偡丅

偝傕側偄偲丄妱傝崬傒張棟偑廔椆偟偨捈屻偵傆偨偨傃妱傝崬傒偑庴偗晅偗傜傟偰偟傑偄傑偡丅

偲偙傠偱丄俶俵俬偺傎偆偼丄偝偒傎偳偺暥復偵偁傝傑偟偨傛偆偵丄値倕倗倎倲倝倴倕丂倕倓倗倕亅倲倰倝倗倗倕倰倕倓偱偡丅偙偪傜偺傎偆偼俬俶俿偲偪偑偭偰丄怣崋偺値倕倗倎倲倝倴倕亅倕倓倗倕偮傑傝怣崋偺壓偑傝僄僢僕偺傒偑桳岠偲偄偆偙偲偱偡丅

偄偪偳怣崋偑俫倝倗倛偵側偭偰偐傜偱側偄偲丄傆偨偨傃専弌偝傟傞偙偲偼側偄丄偲偄偆偙偲偵側傝傑偡偐傜丄偦傟側傜偽丄儅僗僋偱偒側偔偰傕丄妱傝崬傒張棟偺娫偵廳偹偰庴偗晅偗傜傟傞偙偲偼側偄丄偲偄偆偙偲偵側傝傑偡丅

偲偙傠偱乮偲丄偲偙傠偱偽偐傝偑懕偒傑偡偑乯俶俵俬偼俬俶俿偲摨偠偔丄柦椷偺嵟屻偺僋儘僢僋偺忋偑傝僄僢僕偱僒儞僾儕儞僌偝傟傞偲偺偙偲側偺偵丄偦偺堦曽偱丄俶俵俬偼偦偺怣崋偺壓偑傝僄僢僕偺傒偑桳岠偲偄偆偺偼丄堦懱偳偆偄偆偙偲側偺偐丠偲偝傜偵媈栤偑晜忋偟偰偔傞偺偱偁傝傑偡偑丄偙傟偼偍偦傜偔丄倕倓倗倕亅倲倰倝倗倗倕倰倕倓偲偄偆尵梩偵堄枴偑偁傞傛偆側婥偑偟傑偡丅

懡暘丄俶俵俬偺壓偑傝僄僢僕偑僩儕僈偲側偭偰丄俠俹倀撪晹偺偳偙偐偵俶俵俬偺擖椡偑儔僢僠偝傟丄偦傟偑柦椷偺嵟屻偺僋儘僢僋偱専弌偝傟傞丄偺偱偼側偄偐偲峫偊傜傟傑偡丅

偦傟偵偮偄偰偼丄乵戞係俁俆夞乶偱偛徯夘偟偨倅俉侽偺乽俢倎倓倎倱倛倕倕倲乿偵丄師偺傛偆側愢柧偑偁傝傑偟偨丅

Although NMI_ is an asynchronous input,to guarantee its being recognized on the following machine cycle,NMI_'s falling edge must occur no later than the rising edge of the clock cycle preceding the last state of any instruction cycle(TLI).

俶俵俬偼丄旕摨婜擖椡乮偍偦傜偔俠俹倀僋儘僢僋偲摨婜偟偰偄側偔偰偄偄丄偲偄偆堄枴乯偩偗傟偳傕丄偦偺擖椡偵懕偔儅僔儞僒僀僋儖偱擣幆偝傟傞偨傔偵偼丄柦椷偺嵟屻偺僋儘僢僋偺忋偑傝僄僢僕傛傝傕慜偵俶俵俬偺壓偑傝僄僢僕偑側偗傟偽側傜側偄丄偲彂偄偰偁傝傑偡丅

俶俵俬偼儗儀儖偱偼側偔偰丄壓偑傝僄僢僕偑僩儕僈偵側傞偺偩偗傟偳丄偦傟偑俠俹倀偵傛偭偰僒儞僾儕儞僌偝傟傞偺偼丄偦傟傛傝傕偁偲偵偁傞柦椷偺嵟屻偺僋儘僢僋偺忋偑傝僄僢僕側偺偱丄偦偺僋儘僢僋偺忋偑傝僄僢僕傛傝傕偁偲偵俶俵俬乮偺壓偑傝僄僢僕乯偑擖椡偝傟偨傜丄師偺柦椷偺嵟屻偺僋儘僢僋偵側傜側偄偲丄偦偺俶俵俬偼擣幆偝傟側偄傛丄偲偄偆偙偲偱偟傚偆丅

崱夞偼僗僥僢僾摦嶌偺偨傔偺俬俶俿夞楬偵偮偄偰愢柧傪偡傞偮傕傝偩偭偨偺偱偡偑丄偮偄俶俵俬偵偼傑偭偰偟傑偭偰丄帪娫偑側偔側偭偰偟傑偄傑偟偨丅

俬俶俿偍傛傃僗僥僢僾夞楬偵偮偄偰偼傑偨師夞偵丄偲偄偆偙偲偵偄偨偟傑偡丅

俀侽侾侽丏俀丏俀侽倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞