(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞侾侽俁夞乶

仠俻倕弌椡偵偮偄偰丄僞僀儈儞僌僠儍乕僩偱愢柧偟傑偡

慜夞丄僞僀儈儞僌敪惗夞楬偺丄俈係俫俠俈係傪巊偭偨俻倕弌椡夞楬偑娫堘偭偰偄傞丄偲彂偒傑偟偨丅

傕偆堦搙僞僀儈儞僌僷儖僗偺敪惗夞楬乮晹暘乯傪嵞宖偟傑偡丅

偙偺夞楬偼俿侾俆偺偲偒偩偗丄惓偟偄弌椡偑摼傜傟傑偣傫丅

僞僀儈儞僌僠儍乕僩偱愢柧偟傑偡丅

柦椷偺僞僀儈儞僌僠儍乕僩傪棙梡偟偨偨傔丄俿係偐傜偺僠儎乕僩偵側偭偰偄傑偡丅

俻倎乣俻倓偑俈係俫俠侾俇侾偐傜偺弌椡怣崋偱丄俻倕偼乽婜懸偝傟傞乿俈係俫俠俈係偐傜偺弌椡怣崋偱偡丅

俈係俫俠侾俇侾偺倫倝値侾俆偐傜偼乽俿侾俆乿偺婜娫偵忋埵寘傊偺僉儍乕儕乕僷儖僗偑弌椡偝傟傑偡丅

僉儍乕儕乕弌椡偑俿侾俆偐傜俿侾俇偵側傞弖娫偵弌偰偔傟傟偽丄栤戣偼側偐偭偨偺偱偡偑丄偦偆偱偼側偐偭偨偲偙傠偵儈僗偺尨場偑偁傝傑偟偨丅

僉儍乕儕乕僷儖僗偼俿侾俆偵側傞偲摨帪偵丄棫偪忋偑傝丄俿侾俆偺婜娫拞俫偵側偭偰偄傑偡丅

偙偺怣崋傪俈係俫俠俈係偺俠俲擖椡偵偟偰偄傑偟偨丅

俈係俫俠俈係偼俠俲偺乽棫偪忋偑傝僄僢僕乿偱擖椡傪儔僢僠偟偰丄弌椡傪曄壔偝偣傑偡丅

偲偄偆偙偲偼丄俿侾俆偺棫偪忋偑傝偱丄俻倕偑弌椡偝傟偰偟傑偆偺偱偡乮僞僀儈儞僌僠儍乕僩偺俻倕倃乯丅

俿侾俆偱偡偐傜丄俻倕乣俻倎偼乭侽侾侾侾侾乭偱側偗傟偽側傜側偄偺偵丄乭侾侾侾侾侾乭偵側偭偰偟傑偄傑偡乮俿侾俆偱偼側偔偰丄俿俁侾偱偡乯丅

偳偆偡傟偽傛偄偐偲偄偆偲丄俈係俫俠俈係偺俠俲偲偟偰丄俈係俫俠侾俇侾偺倫倝値侾俆偺弌椡傪偦偺傑傑巊偆偺偱偼側偔偰丄偦偺弌椡傪俈係俫俠侽係偱斀揮偝偣偨怣崋傪巊偊偽傛偄偺偱偡丅

偨偩丄栤戣偑侾偮偩偗偁傝傑偡丅

偙偺僞僀儈儞僌敪惗夞楬偼俵們倢倰怣崋偱僋儕傾偡傞傛偆偵側偭偰偄傑偡丅

傕偟傕俿侾俆偺棫偪忋偑傝偱俵們倢倰偑擖椡偝傟傞偲丄崲偭偨偙偲偑偍偒傞壜擻惈偑偁傝傑偡丅

僞僀儈儞僌僠儍乕僩偺壓偺晹暘偑偦傟偱偡丅

俿侾俆偺偲偒偵敪惗偡傞俵們倢倰偼丄俿侾俆偑棫偪忋偑偭偰偐傜弌椡偝傟傑偡偐傜丄俈係俫俠侾俇侾偺倫倝値侾俆偐傜僉儍儕乕僷儖僗偼弌偰偟傑偭偨偁偲偵側傝傑偡丅

僉儍儕乕僷儖僗偺棫偪壓傝乮偮傑傝俈係俫俠俈係偺俠俲擖椡偺棫偪忋偑傝乯偼丄俵們倢倰怣崋乮俈係俫俠侾俇侾偲俈係俫俠俈係偺僋儕傾怣崋乯偲摨帪偱偼側偔偰丄俈係俫俠侾俇侾偺弌椡抶墑帪娫偩偗抶傟傑偡丅

偲偄偆偙偲偼丄俵們倢倰偵傛偭偰俻倕乣俻倎偑乭侽侽侽侽侽乭偵側偭偨捈屻偵丄俈係俫俠俈係偺俠俲擖椡乮棫偪忋偑傝僄僢僕乯偑敪惗偡傞偨傔丄俻倕乣俻倎偼乭侾侽侽侽侽乭偵側偭偰偟傑偄傑偡乮偲悇應偝傟傑偡乯丅

幚偼丄乽偮偔傞俠俹倀乿夞楬偱偼丄俵們倢倰偼俿値婜娫偺値亖嬼悢偺棫偪忋偑傝偱敪惗偡傞傛偆偵偟偰偄傑偡偐傜丄幚嵺偵偼偦偺傛偆側偙偲偑偍偒傞怱攝偼偁傝傑偣傫乮偲巚偄傑偡乯丅

偝傜偵丄偙偺栤戣偼俿侾俆偺偲偒偵偩偗敪惗偡傞壜擻惈偑偁傝傑偡偑丄岾偄側偙偲偵丄彮側偔偲傕俿侾俆偺偲偒偵俵們倢倰傪敪惗偝偣傞柦椷夞楬偼偁傝傑偣傫丅

偱偡偗傟偳丄擮偺偨傔偵丄偲偄偆偙偲偱丄僞僀儈儞僌僠儍乕僩偺壓偺晹暘偺傛偆側怱攝傕夞旔偡傞傛偆偵丄岺晇偟偨夞楬偵捈偟傑偟偨丅

俠俴俲偺屻敿偺俴偺婜娫偩偗丄僉儍儕乕僷儖僗偑俈係俫俠俈係偵揱偊傜傟傞傛偆偵偟傑偟偨丅

傕偟傕俿侾俆偺偲偒偵俵們倢倰偑擖椡偝傟傞偙偲偱丄俿侾俆偺棫偪忋偑傝晹暘偱岆偭偨僉儍儕乕僷儖僗偑俈係俫俠侾俇侾偐傜弌椡偝傟偨偲偟偰傕丄俈係俫俠侽係偲俈係俫俠侽侽偺僎乕僩偵傛偭偰丄僋儘僢僋偺慜敿晹暘偼丄俈係俫俠俈係偵偼揱傢傝傑偣傫偐傜丄忋偱彂偄偨傛偆側丄乭侽侽侽侽侽乭偑乭侾侽侽侽侽乭偵側偭偰偟傑偆怱攝偼偁傝傑偣傫丅

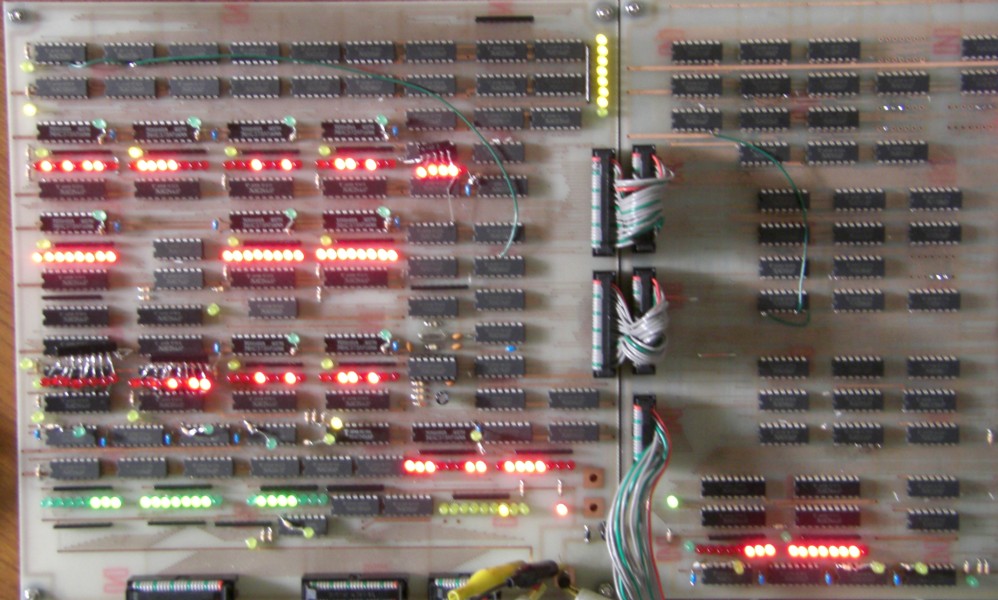

夞楬傪廋惓偟偨屻偵嶣塭偟偨丄倃俿俫俴柦椷偺俿侾俆偺幨恀偱偡丅

傑偨僺儞儃働偵側偭偰偟傑偄傑偟偨偗傟偳丄俴俤俢昞帵偼惓偟偔側傝傑偟偨丅

俀侽侽俉丏侾侽丏俀俇倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞