倁俫俢俴傪懍廗両丂倃俠俋俆侾係係倃俴亄侾俇俵俛丒俽俬俵俵傪巊偭偰倀俽俛僾儘僩僐儖傾僫儔僀僓傪嶌偭偰偟傑偄傑偟偨両

庡栚揑偼嵎偟敆偭偨帠忣偐傜倀俽俛僾儘僩僐儖偺夝愅傪偡傞偙偲偩偭偨偺偱偡偑丄偦偺庤抜偲偟偰慖傫偩偺偑僐儗両

乵戞俉俁夞乶

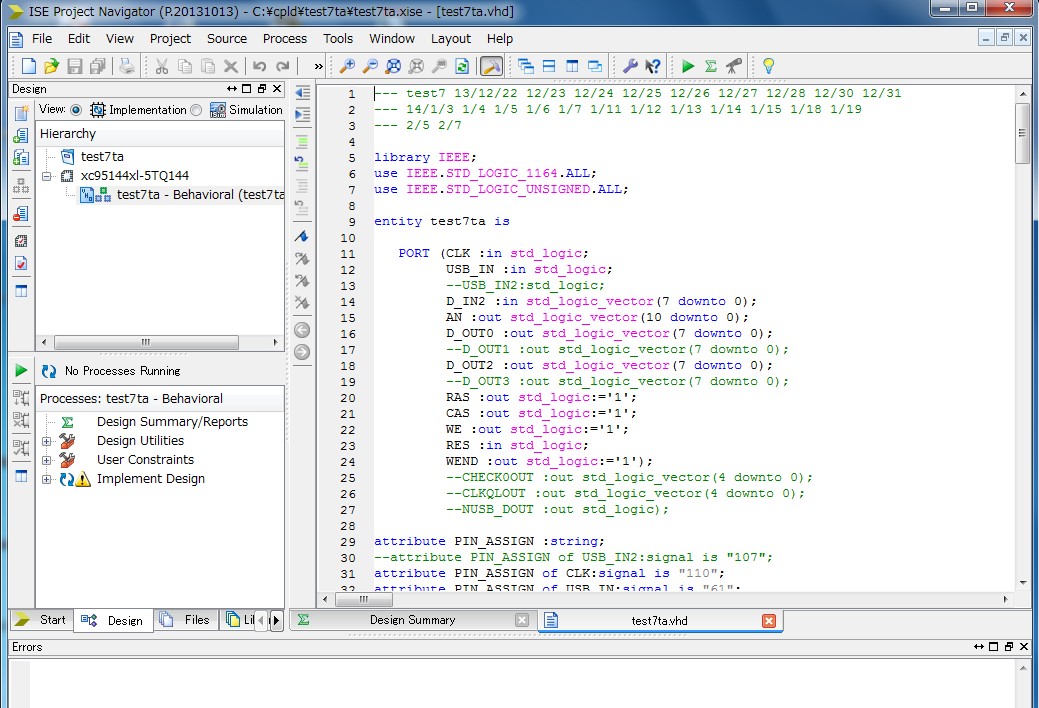

仠倃倝倢倝値倶丂俬俽俤丂俢倕倱倝倗値丂俽倳倝倲倕丂傪巊偆乮俀乯

慜夞偼俬俽俤丂俢倕倱倝倗値丂俽倳倝倲倕偱怴偟偄僾儘僕僃僋僩丄怴偟偄倁俫俢俴僜乕僗僼傽僀儖傪嶌惉偡傞偲偙傠傑偱傪偞偭偲愢柧偟傑偟偨丅

嶌惉搑拞偺倁俫俢俴偼忋彂偒曐懚偡傞偐怴偟偄僼傽僀儖柤傪偮偗偰曐懚偟傑偡丅

師夞俬俽俤丂俢倕倱倝倗値丂俽倳倝倲倕傪婲摦偡傞偲丄慜夞偺僾儘僕僃僋僩偑慖戰偝傟偰偄傑偡偐傜丄偦傟偱傛偗傟偽偦偺傑傑僜乕僗僼傽僀儖傪奐偄偰曇廤嶌嬈偺懕偒傪峴側偄傑偡丅

慡偔暿偺僾儘僕僃僋僩傪奐偄偰暿偺僜乕僗僼傽僀儖偺曇廤嶌嬈傪峴側偆偙偲傕偱偒傑偡丅

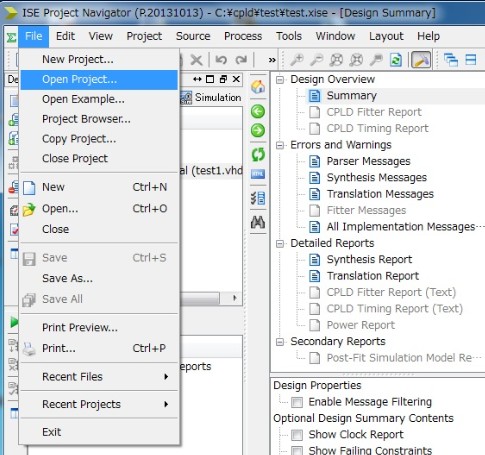

埲慜偵嶌嬈偟偨暿偺僾儘僕僃僋僩傪奐偔偵偼丄嵍忋偺俥倝倢倕傪僋儕僢僋偟偰俷倫倕値丂俹倰倧倞倕們倲丏丏丏傪慖戰偟傑偡丅

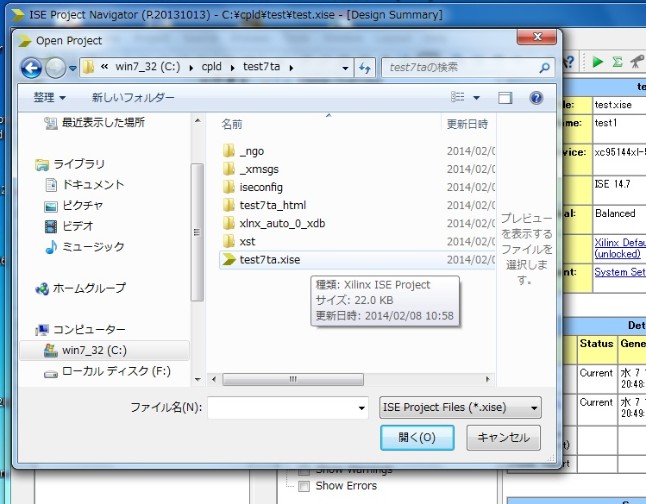

僼僅儖僟僣儕乕偺拞偐傜栚揑偺僾儘僕僃僋僩偑偁傞僼僅儖僟傪慖戰偟傑偡丅

奼挘巕偑倶倝倱倕偺僼傽僀儖偑僾儘僕僃僋僩僼傽僀儖偱偡丅

偦偺僼傽僀儖傪慖戰偟偰乵奐偔乶傪僋儕僢僋偟傑偡丅

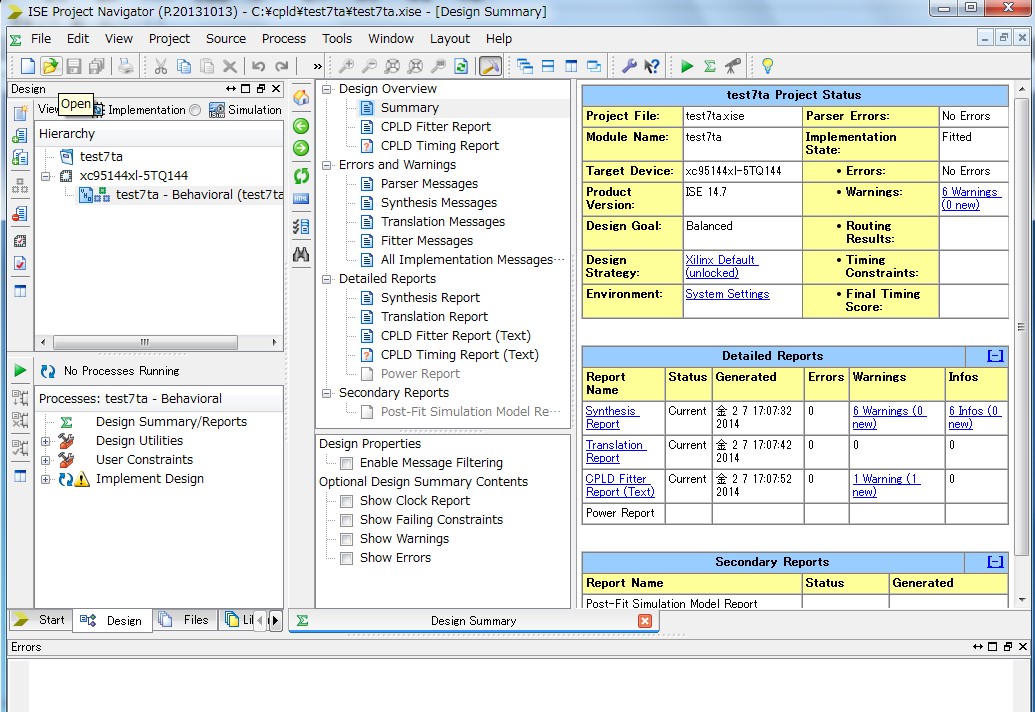

栚揑偺僾儘僕僃僋僩偑奐偒傑偡丅

崱搙偼忋偺僣乕儖僶乕偺嵍偐傜俀斣栚偵偁傞乽僼僅儖僟傪奐偔傾僀僐儞乿傪僋儕僢僋偟傑偡丅

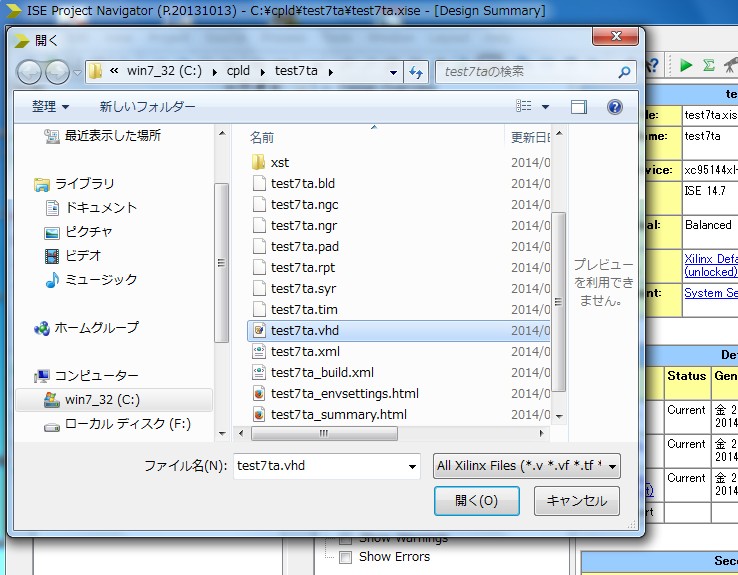

偝偒傎偳偲摨偠僼僅儖僟偑奐偒傑偡偑丄崱搙偼戲嶳偺庬椶偺僼傽僀儖偑昞帵偝傟傑偡丅

奼挘巕偑倴倛倓偺僼傽僀儖偑倁俫俢俴僜乕僗僼傽僀儖偱偡丅

偦偺僼傽僀儖傪慖戰偟偰乵奐偔乶傪僋儕僢僋偟傑偡丅

倁俫俢俴僜乕僗僼傽僀儖偑奐偒傑偡丅

偙偺忬懺偱晛捠偺僪僉儏儊儞僩偺嶌惉偲慡偔摨偠姶妎偱曇廤嶌惉嶌嬈傪峴側偆偙偲偑偱偒傑偡丅

倁俫俢俴僜乕僗僼傽僀儖偑姰惉偟偨傜丄偄傛偄傛幚憰夁掱偱偡丅

倁俫俢俴僜乕僗僼傽僀儖偐傜幚嵺偵俠俹俴俢傗俥俹俧俙偵彂偒崬傓偨傔偺僼傽僀儖傪惗惉偡傞岺掱偱偡丅

榑棟崌惉偲偐偲尵偆傛偆偱偡丅

僐儞僷僀儖偺傛偆側傕偺偱偟傚偆丅

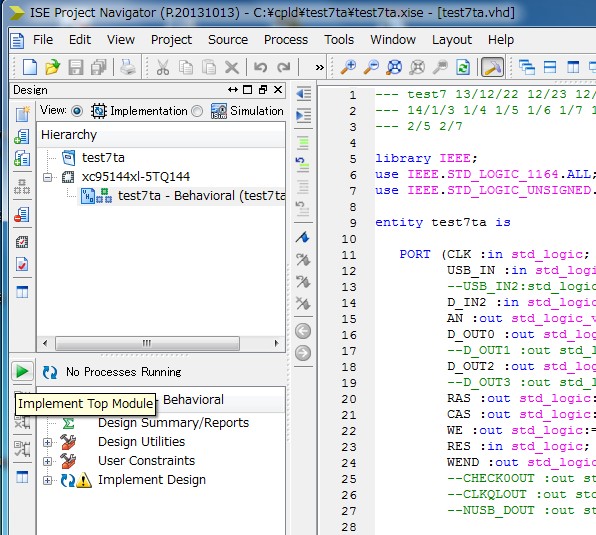

嵍懁拞傎偳偺椢偺塃岦偒嶰妏傾僀僐儞傪僋儕僢僋偟傑偡丅

俹俬俠偺俵俹俴俙俛丂俬俢俤側偳偲摨偠偱堦搙幚峴嵪傒偺僜乕僗僼傽僀儖偼偦偺傑傑偱偼擇搙偲幚峴偟偰偔傟傑偣傫丅

彮偟偱傕彂偒姺偊傟偽乮僐儊儞僩峴傪捛壛丄彂偒姺偊偡傞偩偗偱傕乯嵞幚峴偟偰偔傟傑偡丅

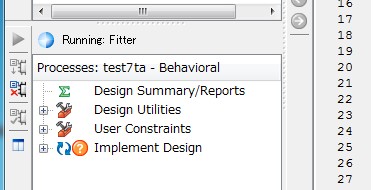

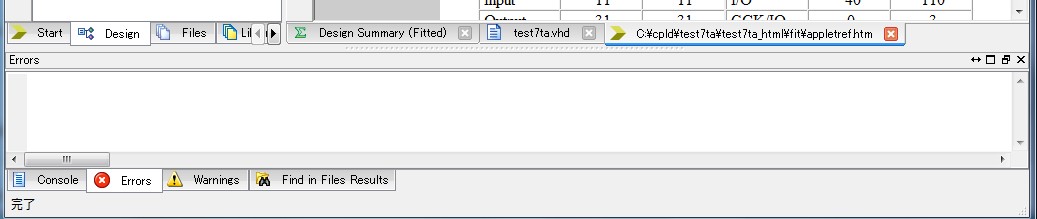

僾儘僙僗偺幚峴拞偱偡丅

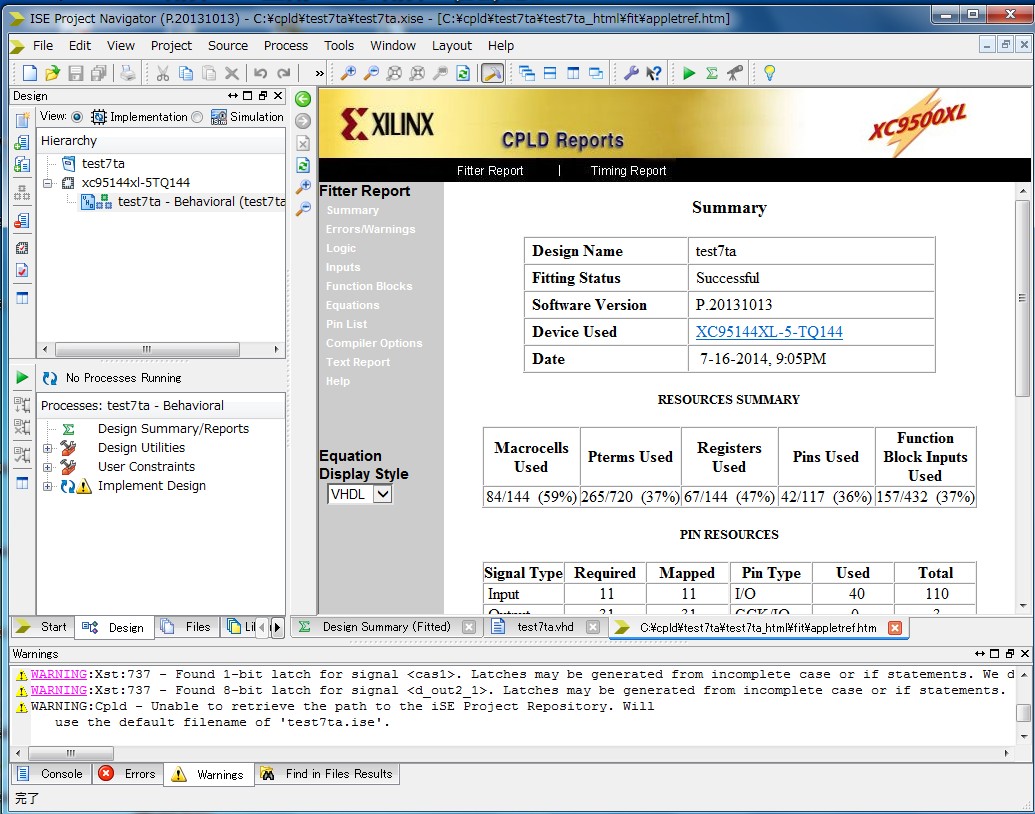

柍帠姰椆偡傞偲偙乕傫側嬄乆偟偄儗億乕僩偑昞帵偝傟傑偡丅

偨偄偰偄戲嶳偺倂俙俼俶俬俶俧偑昞帵偝傟傑偡丅

榑棟偺慻傒棫偰曽偵傛偭偰偼堄恾偟側偄儔僢僠偑惗惉偝傟偰偟傑偆偙偲偑偁偭偰丄偦傟偵懳偡傞寈崘偑懡偄傛偆偱偡丅

堄恾偟偰彂偄偨応崌偱傕寈崘偑弌偰偟傑偄傑偡丅

夞楬偵傛偭偰偼儔僢僠摦嶌偱偼傑偢偄応崌傕弌偰偒傑偡偐傜寈崘偼柺搢偱傕慡晹妋擣偡傋偒偱偟傚偆丅

倂俙俼俶俬俶俧偼寈崘偱偡偐傜丄栚揑僼傽僀儖偺惗惉偼峴側傢傟傑偡丅

壗偐栤戣偑偁傞応崌偵偼僄儔乕儊僢僙乕僕偑昞帵偝傟傑偡丅

俤倰倰倧倰僞僽傪僋儕僢僋偟偰壗傕昞帵偝傟側偗傟偽僄儔乕偼偁傝傑偣傫丅

偟偐偟摿偵姷傟側偄偆偪偼偦傟偙偦嶳傎偳僄儔乕偑昞帵偝傟偰偟傑偄傑偡丅

偨偄偰偄偼偪傚偭偲棊偪拝偄偰峫偊偰傒傟偽棟桼偑擺摼偱偒傞僄儔乕儊僢僙乕僕偱偡偑丄拞偵偼堄枴晄柧偺僄儔乕儊僢僙乕僕偑弌傞偙偲偑偁偭偰峫偊偝偣傜傟偰偟傑偄傑偡丅

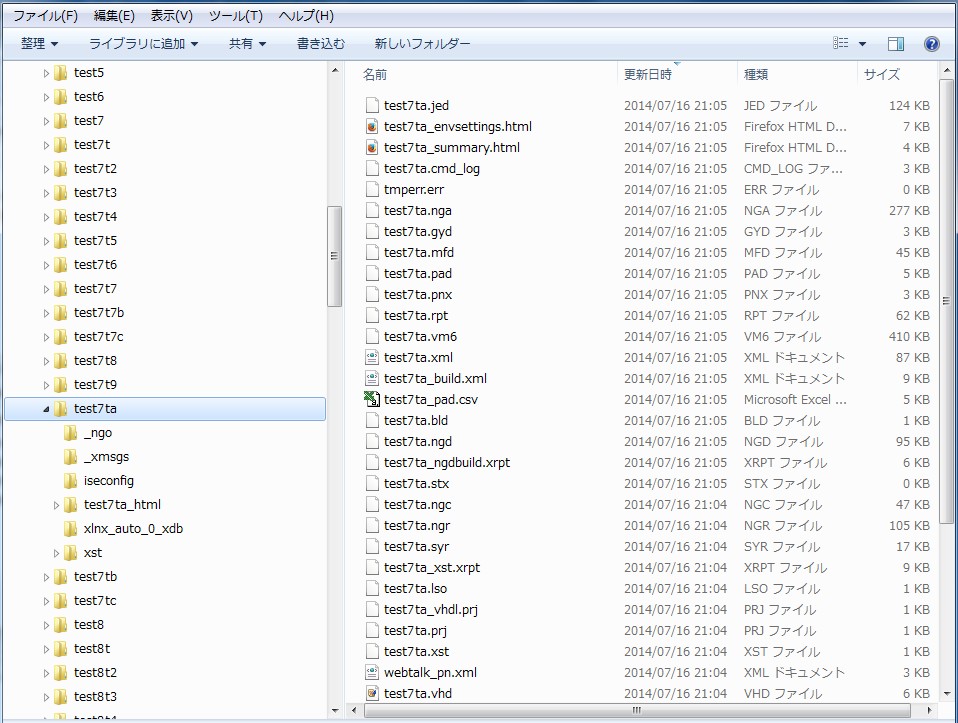

栚揑僼傽僀儖偑柍帠惗惉偝傟傞偲丄嶳偺傛偆側僼傽僀儖偑嶌惉偝傟偰偄傑偡丅

俠俹俴俢偺応崌偵偼奼挘巕偑倞倕倓偺僼傽僀儖偑彂偒崬傒偵巊偆僼傽僀儖偱偡丅

俠俹俴俢亄俽俬俵俵傪巊偭偰倀俽俛僾儘僩僐儖偺夝愅傪両乵戞俉俁夞乶

俀侽侾係丏俈丏侾俇倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞