〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜

いつか使うことになるだろうと思ってはいたのですが。

何を今頃になって、というようなものですが。

ようやく本気で、CPLDと四つに取り組みます。

〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜

[第43回]

●82C55を追加しました

1ヶ月の1/3がお休みというとんでもない超大型連休も本日で終わりです。

皆様はいかがお過ごしでしたでしょうか。

私はといいますと、何しろ滅多に無い機会ですので真性ワーカーホリックの本領を発揮しまして、業務にまい進しておりました。

おかげでそこそこ成果があげられたと思います。

その成果につきましてはこれから当ブログ風にて少しずつお伝えしていきたいと思います。

しかし。

成果はあがっているのですけれど、それを整理して写真や図版もまじえて書こうとしますと、結構時間がかかって思うように進められません。

相変わらずちまちまと、また休み休みの連載となってしまいます。

気長なお付き合いをお願いいたします。

EPM7128SLC84を使ったPIC7セグメントLED/5X5キー/PICUSBIFボードも前回めでたく完成いたしました。

このボードは近いうちに製品として販売を開始の予定です。

今回はEPM7032SLC44を使ったPICUSBIFボード([第21回])の機能追加について書きます。

同ボードはCPLD回路の小手調べとしてとりあえず作ってみた簡単なボードなので、EPM7032SLC44の端子にもVHDLプログラムにも、そして基板スペースとしても余裕があります。

ちょいと勿体無いと思いましたので、そこに82C55回路を追加してしまいました。

下は回路図です。

回路図の下側半分弱が追加回路ですが、EPM7032SLC44に注目すると、82C55のCS端子への出力を追加しただけです。

EPM7032SLC44としては軽微な追加ということになりますでしょう。

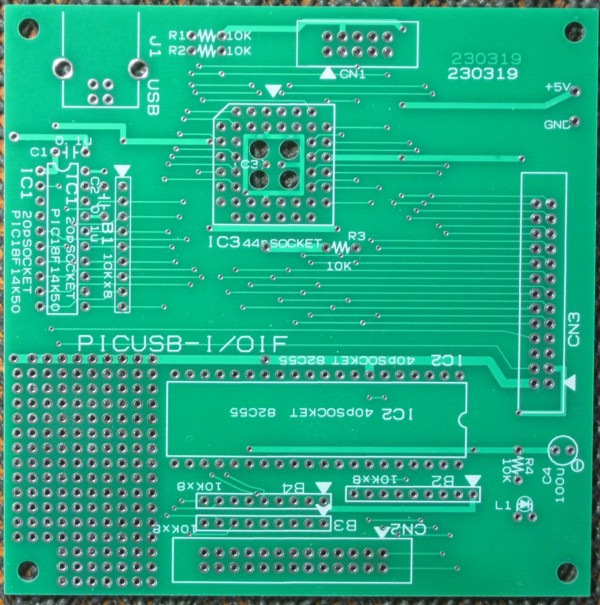

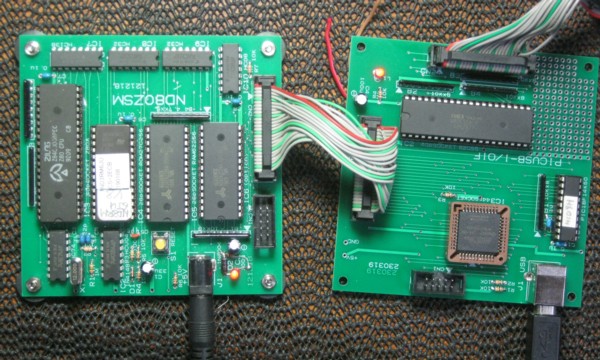

新しく作った基板です。

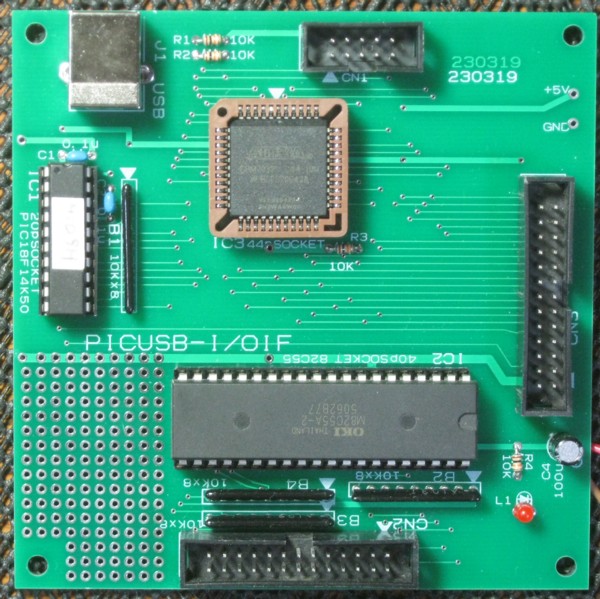

パーツを実装しました。

ND80ZSMに接続して動作テストをしました。

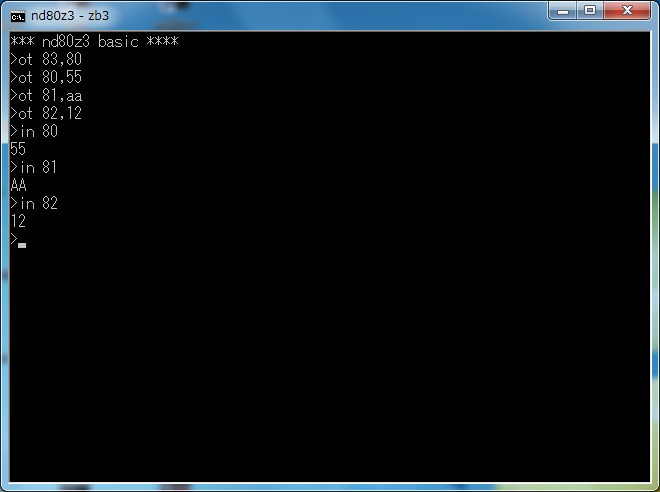

USB接続したWindows7のコマンドプロンプト画面です。

追加したVHDLプログラムでは、82C55はND80Z3.5と同じようにI/Oアドレス80〜83に割り当てました。

ot、inはZB3BASICのマシン語コマンドです。

otはoutコマンドです。

アドレス83に80をoutして全ポートを出力に設定。

アドレス80(Aポート)に55を出力。

アドレス81(Bポート)にAAを出力。

アドレス82(Cポート)に12を出力しました。

82C55は出力に設定したポートに対してINを実行すると、そのときの出力データがそのまま読み出されます。

アドレス80〜82に対してINを実行した結果、上で出力した値が正しく読み出せました。

もし82C55回路に問題があれば、FFが読み出されたりすることになります。

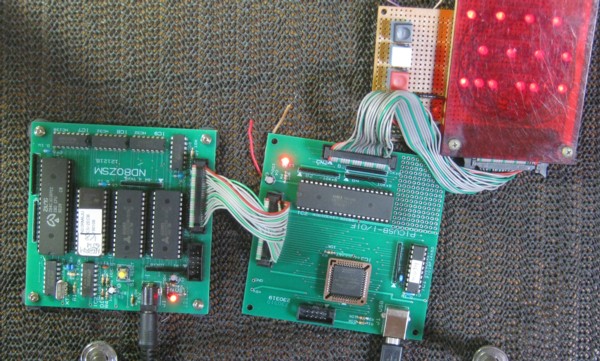

実際に82C55の出力コネクタにLED回路をつないで出力を確認しました。

LED表示回路の部分をアップしました。

このテストボードは随分長い間使っていますので、アクリル板が傷だらけです。

出力にLEDのカソードをつないでいますから、Hのとき消灯、Lのとき点灯します。

上からAポート、Bポート、Cポート、左がビット7、右がビット0です。

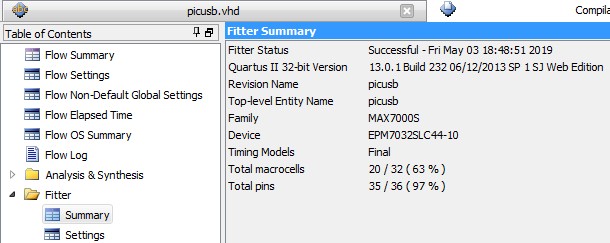

VHDLプログラムです。