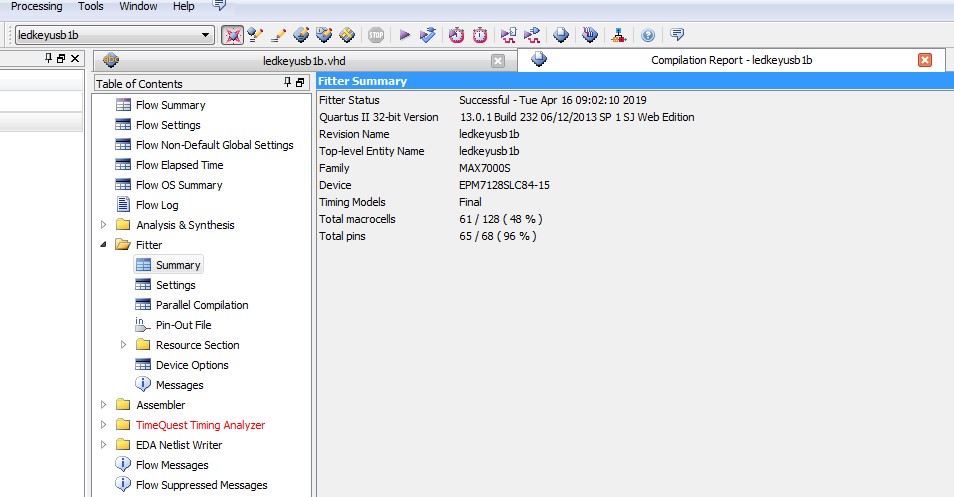

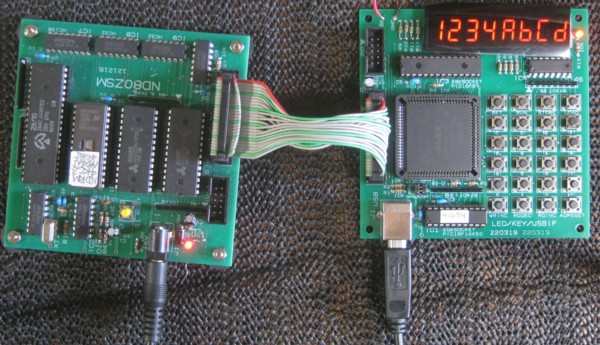

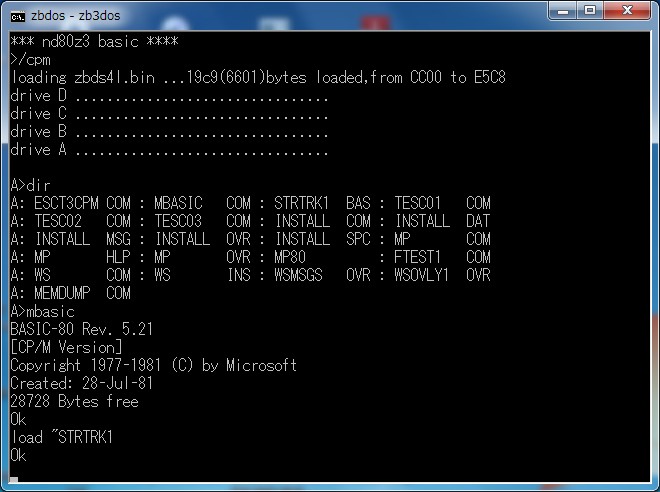

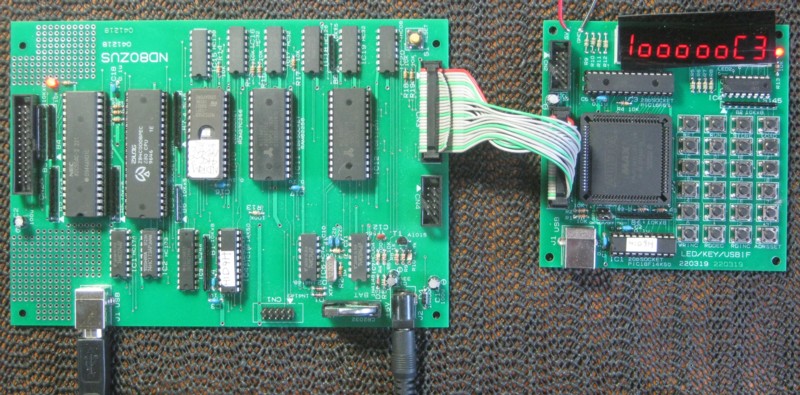

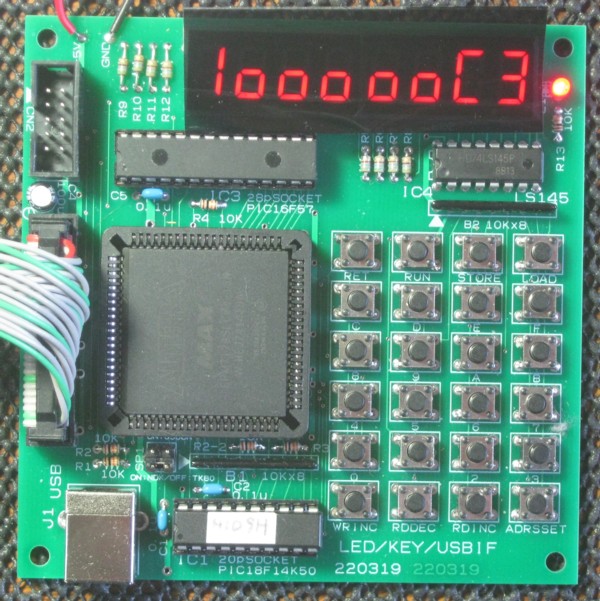

--7segx8 and 5x5 key usb interface 19/4/10

-- from ledkeyusb1a

-- 4/11 4/12 4/13 4/15 4/16

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

library ARITHMETIC;

use ARITHMETIC.std_logic_arith.all;

entity ledkeyusb1b is

PORT (

KEYOUT:out std_logic_vector(2 downto 0);

KEYIN:in std_logic_vector(7 downto 0);

AIN:in std_logic_vector(7 downto 0);

DINOUT:inout std_logic_vector(7 downto 0);

PIC16READ:in std_logic;

PIC16AD:in std_logic_vector(1 downto 0);

LDATAREADY:out std_logic;

LDATAOUT:out std_logic_vector(3 downto 0);

--PIC18RC:out std_logic_vector(7 downto 0);

--PIC18RB4:out std_logic;

--PIC18RB6:out std_logic;

RC3_RC0:inout std_logic_vector(3 downto 0);

RB6_RC4:in std_logic_vector(2 downto 0);

RC7_RC5:out std_logic_vector(2 downto 0);

--

USBON:in std_logic;

TKND:in std_logic;

P25:in std_logic;

PIC16RA3:in std_logic;--not used

CK12MIN:in std_logic;

RESETIN:in std_logic;

CK12MOUT:out std_logic;

CK12MOUT2:out std_logic;

RESETOUT:out std_logic;

P21:in std_logic;

P52:in std_logic;

P65:in std_logic;

P67:in std_logic;

P69:in std_logic;

IOR:in std_logic;

IOW:in std_logic);

end ledkeyusb1b;

architecture rtl of ledkeyusb1b is

signal ldtactiv:std_logic;

signal readyreset:std_logic;

signal ldatareadywk:std_logic;

signal keyoutbf:std_logic_vector(2 downto 0);

signal keyinbf:std_logic_vector(7 downto 0);

signal ledadrs:std_logic_vector(2 downto 0);

signal segment:std_logic_vector(7 downto 0);

signal rcwk:std_logic;

signal rcwk2:std_logic_vector(3 downto 0);

begin

--ledadrs & segment data set

process(AIN,IOW)

begin

if AIN(7 downto 3)="10001" and IOW='0' then

ldtactiv<='0';

else ldtactiv<='1';

end if;

end process;

process(ldtactiv)

begin

--

if PIC16READ='0' and PIC16AD="10" then

ldatareadywk<='1';

--

elsif ldtactiv'event and ldtactiv='1' then

ledadrs<=AIN(2 downto 0);

segment<=DINOUT;

ldatareadywk<='0';--

end if;

end process;

LDATAREADY<=ldatareadywk;

--ledadrs & segment data out

process(PIC16READ,PIC16AD)

begin

if PIC16READ='0' then

if PIC16AD="00" then

LDATAOUT<=segment(3 downto 0);

elsif PIC16AD="01" then

LDATAOUT<=segment(7 downto 4);

elsif PIC16AD="10" then

LDATAOUT(2 downto 0)<=ledadrs;

readyreset<='0';

else

LDATAOUT<="1111";

readyreset<='1';

end if;

end if;

end process;

--key in

process(AIN,IOW,IOR)

begin

if AIN(7 downto 2)="100111" and IOW='0' then

DINOUT<="ZZZZZZZZ";

if DINOUT(0)='1' then

keyoutbf(0)<='Z';

elsif DINOUT(0)='0' then

keyoutbf(0)<='0';

end if;

if DINOUT(1)='1' then

keyoutbf(1)<='Z';

elsif DINOUT(1)='0' then

keyoutbf(1)<='0';

end if;

if DINOUT(2)='1' then

keyoutbf(2)<='Z';

elsif DINOUT(2)='0' then

keyoutbf(2)<='0';

end if;

elsif AIN(7 downto 2)="100111" and IOR='0' then

keyinbf<=KEYIN;

DINOUT<=keyinbf;

elsif AIN(7 downto 2)="100101" and IOR='0' then

DINOUT(7)<=TKND;

--USB PIC to CPU

if USBON='0' then

DINOUT(6 downto 4)<=RB6_RC4;

DINOUT(3 downto 0)<=RC3_RC0;

end if;

else

DINOUT<="ZZZZZZZZ";

end if;

end process;

--USB CPU to PIC

process(IOW)

begin

if AIN(7 downto 2)="100110" and IOW='0' then

rcwk<=DINOUT(3);

RC7_RC5<=DINOUT(2 downto 0);

elsif AIN(7 downto 2)="100101" and IOW= '0' then

rcwk2<=DINOUT(3 downto 0);

end if;

end process;

process(rcwk)

begin

if rcwk= '0' then

RC3_RC0<=rcwk2;

else

RC3_RC0<="ZZZZ";

end if;

end process;

--

KEYOUT<=keyoutbf;

CK12MOUT<=CK12MIN;

CK12MOUT2<=CK12MIN;

RESETOUT<=RESETIN;

-- PIC18RB6<=ldtactiv;

-- PIC18RC(2 downto 0)<=ledadrs;

end rtl;

|